- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67328 > 5962-8967402XX (CIRRUS LOGIC INC) 1-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 PDF資料下載

參數(shù)資料

| 型號: | 5962-8967402XX |

| 廠商: | CIRRUS LOGIC INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

| 封裝: | CERAMIC, LCC-44 |

| 文件頁數(shù): | 9/50頁 |

| 文件大小: | 520K |

| 代理商: | 5962-8967402XX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

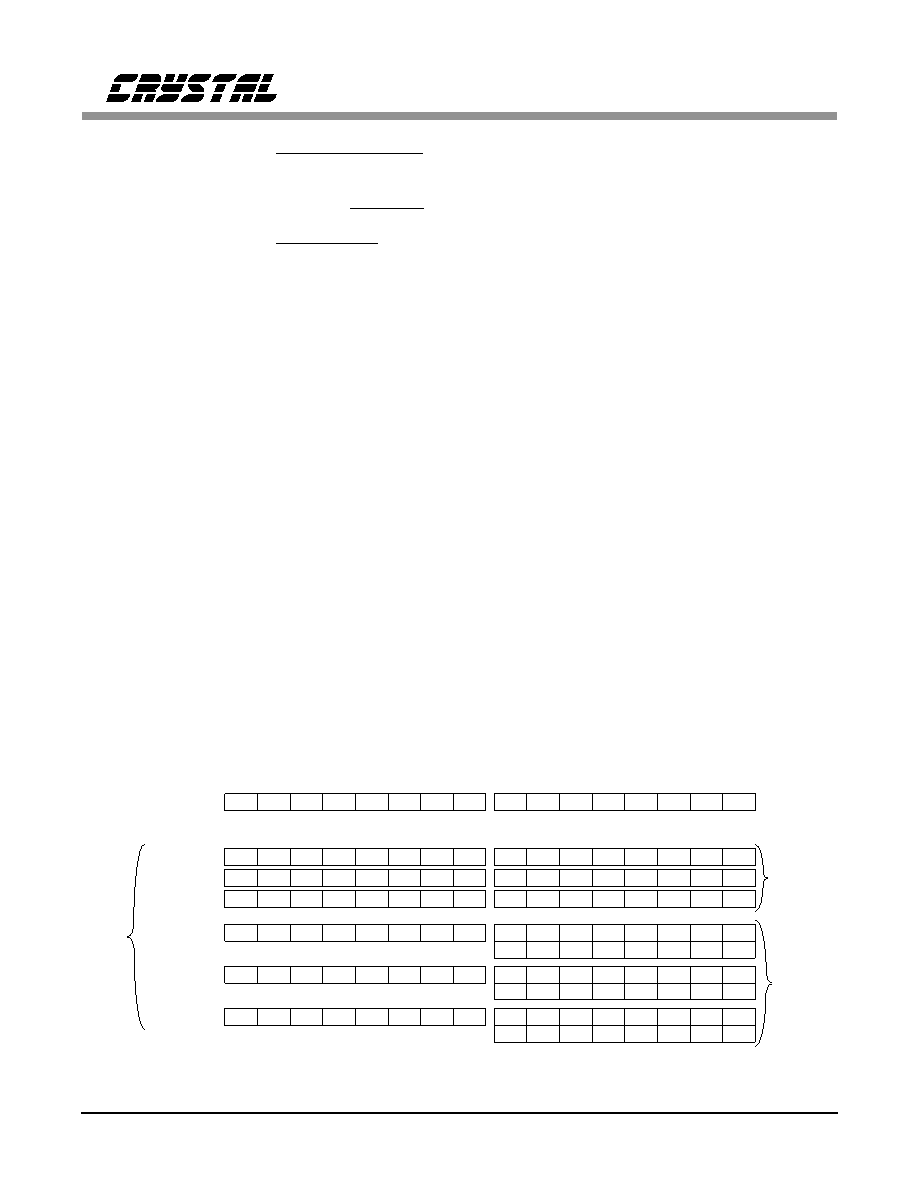

To interface with a 16-bit data bus, the BW input

to the CS5012A/14/16 should be held high and

all data bits (12, 14 and 16 for the CS5012A,

CS5014 and CS5016 respectively) read in paral-

lel on pin s D4-D15 (CS5012A), D2-D15

(CS5014), or D0-D15 (CS5016). With an 8-bit

bus, the converter’s result must be read in two

portions. In this instance, BW should be held low

and the 8 MSB’s obtained on the first read cycle

following a conversion. The second read cycle

will yield the remaining LSB’s (4, 6 or 8 for the

CS5012A/14/16 respectively) with 4, 2 or 0 trail-

ing zeros. Both bytes appear on pins D0-D7. The

upper/lower bytes of the same data will continue

to toggle on subsequent reads until the next con-

version finishes. Status bit S2 indicates which

byte will appear on the next data read operation.

The CS5012A/14/16 internally buffer their output

data, so data can be read while the devices are

tracking or converting the next sample. There-

fore, retrieving the converters’ digital output

requires no reduction in ADC throughput. Ena-

bling

th e

3-st ate

outputs

whil e

the

CS5012A/14/16 is converting will not introduce

conversion errors. Connecting CMOS logic to the

digital outputs is recommended. Suitable logic

families include 4000B, 74HC, 74AC, 74ACT,

and 74HCT.

PIN

STATUS BIT

STATUS

DEFINITION

D0

S0

END OF CONVERSION

Falls upon completion of a conversion,

and returns high on the first subsequent read.

D1

S1

RESERVED

Reserved for factory use.

D2

S2

LOW BYTE/HIGH BYTE

When data is to be read in an 8-bit format (BW=0),

indicates which byte will appear at the output next.

D3

S3

END OF TRACK

When low, indicates the input has been acquired to

the devices specified accuracy.

D4

S4

RESERVED

Reserved for factory use.

D5

S5

TRACKING

High when the device is tracking the input.

D6

S6

CONVERTING

High when the device is converting the held input.

D7

S7

CALIBRATING

High when the device is calibrating.

Table 2. Status Pin Definitions

D7

D0

D5

D3

D2

D1

D6

D4

D12 D11 D10

D9

D8

D15 D14 D13

XX

X

XX

X

S7

S6

S5

S4

S3

S2

S1

S0

8- or 16-Bit

Data Bus

Data

(A0=1)

Status

(A0=0)

"X" Denotes High Impedance Output

XX

X

XX

X

XX

8-Bit Bus

(BW=0)

16-Bit Bus

(BW=1)

B5

B4

B11

B10

B7

B6

B8

B9

CS5012A

CS5014

CS5016

B13

B11

B9

B7

B6

B12

B10

B8

B5

B4

B11

B10

B7

B6

B8

B9

B15

B13

B11

B9

B8

B14

B12

B10

B3

B2

B1

B0

0

00

B5

B4

B3

B2

0

B1

B0

B7

B6

B5

B4

B1

B0

B3

B2

B3

B2

B1

B0

0

00

XX

X

XX

X

XX

B7

B6

B13

B12

B9

B8

B10

B11

B5

B4

B3

B2

0

B1

B0

XX

X

XX

X

XX

B9

B8

B15

B14

B11 B10

B12

B13

B7

B6

B5

B4

B1

B0

B3

B2

CS5016

CS5014

CS5012A

Figure 7. CS5012A/14/16 Data Format

CS5012A, CS5014, CS5016

DS14F6

17

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962-8967401QX | 1-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CDIP40 |

| 5962-8967401XX | 1-CH 14-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

| 5962-8967901QX | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CDIP40 |

| 5962-8967602XX | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

| 5962-8967601XX | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL/PARALLEL ACCESS, CQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962-8967701CA | 制造商:Linear Technology 功能描述:AMPLIFIER-OP AMP 制造商:Texas Instruments 功能描述:OP Amp Quad GP ±22V/44V 14-Pin CDIP Tube 制造商:Texas Instruments 功能描述:OP AMP QUAD GP 22V/44V 14CDIP - Rail/Tube 制造商:Texas Instruments 功能描述:LT1014AMJB QUAD PREC OP AMP |

| 5962-8967702CA | 制造商:Texas Instruments 功能描述:OP Amp Quad GP ±22V/44V 14-Pin CDIP Tube 制造商:Texas Instruments 功能描述:OP AMP QUAD GP 22V/44V 14CDIP - Rail/Tube |

| 5962-8967801XA | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| 5962-8967802XA | 制造商:Rochester Electronics LLC 功能描述:8-BIT QUAD MULT DAC IC - Bulk 制造商:Analog Devices 功能描述: |

| 5962-8967901XC | 制造商:SEI 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。