- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384088 > 73K302L-IH (TDK Corporation) Single-Chip Modem PDF資料下載

參數(shù)資料

| 型號(hào): | 73K302L-IH |

| 廠商: | TDK Corporation |

| 英文描述: | Single-Chip Modem |

| 中文描述: | 單芯片調(diào)制解調(diào)器 |

| 文件頁(yè)數(shù): | 4/29頁(yè) |

| 文件大?。?/td> | 282K |

| 代理商: | 73K302L-IH |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

73K302L

Bell 212A, 103, 202

Single-Chip Modem

4

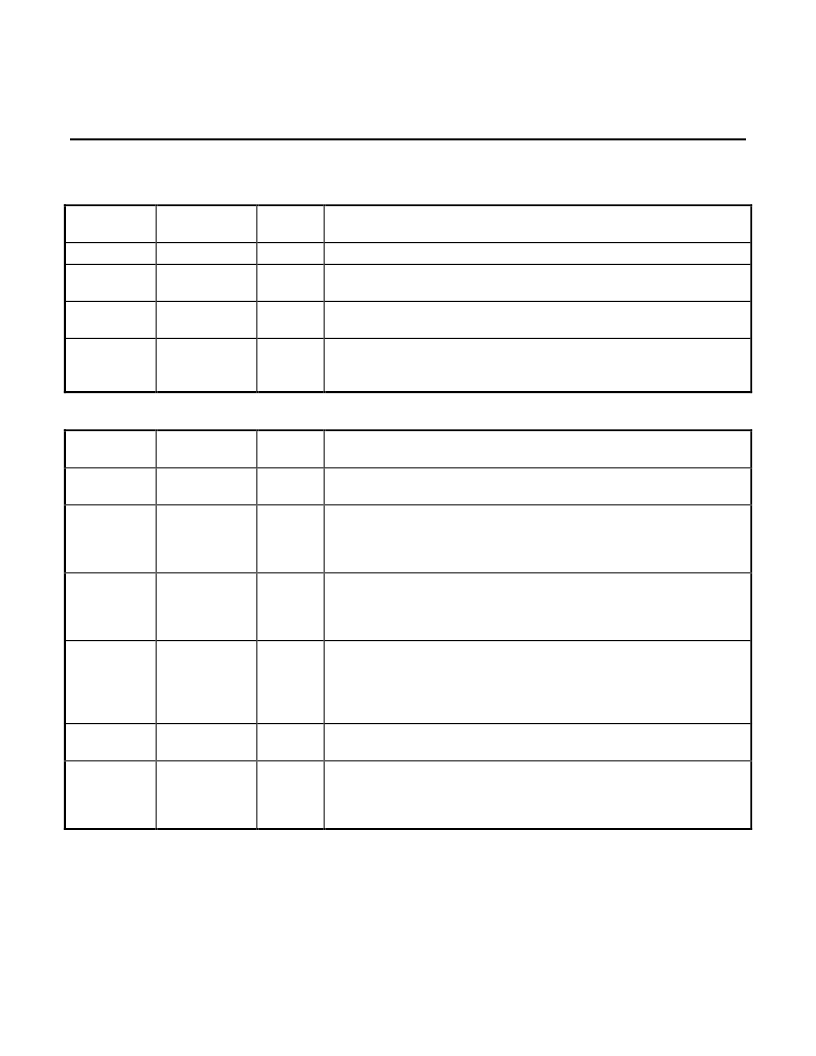

PIN DESCRIPTION

POWER

NAME

PLCC/PIN

DIP NUMBER

TYPE

DESCRIPTION

GND

28

I

System Ground.

VDD

15

I

Power supply input, 5V ±10%. Bypass with 0.1 and 22 μF capacitors

to GND.

VREF

26

O

An internally generated reference voltage. Bypass with 0.1 μF

capacitor to GND.

ISET

24

I

Chip current reference. Sets bias current for op-amps. The chip

current is set by connecting this pin to VDD through a 2 M

resistor.

ISET should be bypassed to GND with a 0.1 μF capacitor.

PARALLEL MICROPROCESSOR INTERFACE

ALE

12

I

Address latch enable. The falling edge of ALE latches the address on

AD0-AD2 and the chip select on

CS

.

AD0-AD7

4-11

I/O

Address/data bus. These bidirectional tri-state multi-plexed lines carry

information to and from the internal registers.

CS

20

I

Chip select. A low on this pin during the falling edge of ALE allows a

read cycle or a write cycle to occur. AD0-AD7 will not be driven and

no registers will be written if

CS

(latched) is not active. The state of

CS

is latched on the falling edge of ALE.

CLK

1

O

Output clock. This pin is selectable under processor control to be

either the crystal frequency (for use as a processor clock) or 16 times

the data rate for use as a baud rate clock in DPSK mode only. The

pin defaults to the crystal frequency on reset.

INT

17

O

Interrupt. This open drain output signal is used to inform the

processor that a detect flag has occurred. The processor must then

read the detect register to determine which detect triggered the

interrupt.

INT

will stay low until the processor reads the detect register

or does a full reset.

RD

14

I

Read. A low requests a read of the 73K302L internal registers. Data

cannot be output unless both

RD

and the latched

CS

are active or low.

RESET

25

I

Reset. An active high signal on this pin will put the chip into an inactive

state. All control register bits (CR0, CR1, Tone) will be reset. The

output of the CLK pin will be set to the crystal frequency. An internal

pull down resistor permits power on reset using a capacitor to VDD.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 73K302L-IP | Single-Chip Modem |

| 74ALVCH2245 | Low Voltage Bidirectional Transceiver with Bushold and 26з Series Resistors in B Outputs |

| 74ALVCH2245MTC | 3-Line To 8-Line Decoders/Demultiplexers 16-SOIC -40 to 85 |

| 74ALVCH2245WM | 3-Line To 8-Line Decoders/Demultiplexers 16-SOIC -40 to 85 |

| 74ALVCH2245MTCX | BUS TRANSCEIVER|SINGLE|8-BIT|AVC/ALVC-CMOS|TSSOP|20PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 73K302L-IP | 制造商:TDK 制造商全稱(chēng):TDK Electronics 功能描述:Single-Chip Modem |

| 73K321L | 制造商:TDK 制造商全稱(chēng):TDK Electronics 功能描述:CCITT V.23, V.21 Single-Chip Modem |

| 73K321L-IH | 制造商:TDK 制造商全稱(chēng):TDK Electronics 功能描述:CCITT V.23, V.21 Single-Chip Modem |

| 73K321L-IP | 制造商:TDK 制造商全稱(chēng):TDK Electronics 功能描述:CCITT V.23, V.21 Single-Chip Modem |

| 73K322L | 制造商:TDK 制造商全稱(chēng):TDK Electronics 功能描述:CCITT V.23, V.22, V.21 Single-Chip Modem |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。