- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360360 > 74ABT16543DL (NXP SEMICONDUCTORS) 16-bit latched transceivers with dual enable 3-State PDF資料下載

參數(shù)資料

| 型號: | 74ABT16543DL |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | 16-bit latched transceivers with dual enable 3-State |

| 中文描述: | ABT SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| 封裝: | PLASTIC, SSOP3-56 |

| 文件頁數(shù): | 4/12頁 |

| 文件大?。?/td> | 90K |

| 代理商: | 74ABT16543DL |

Philips Semiconductors

Product specification

74ABT16543

74ABTH16543

16-bit latched transceivers with dual enable

(3-State)

1998 Feb 27

4

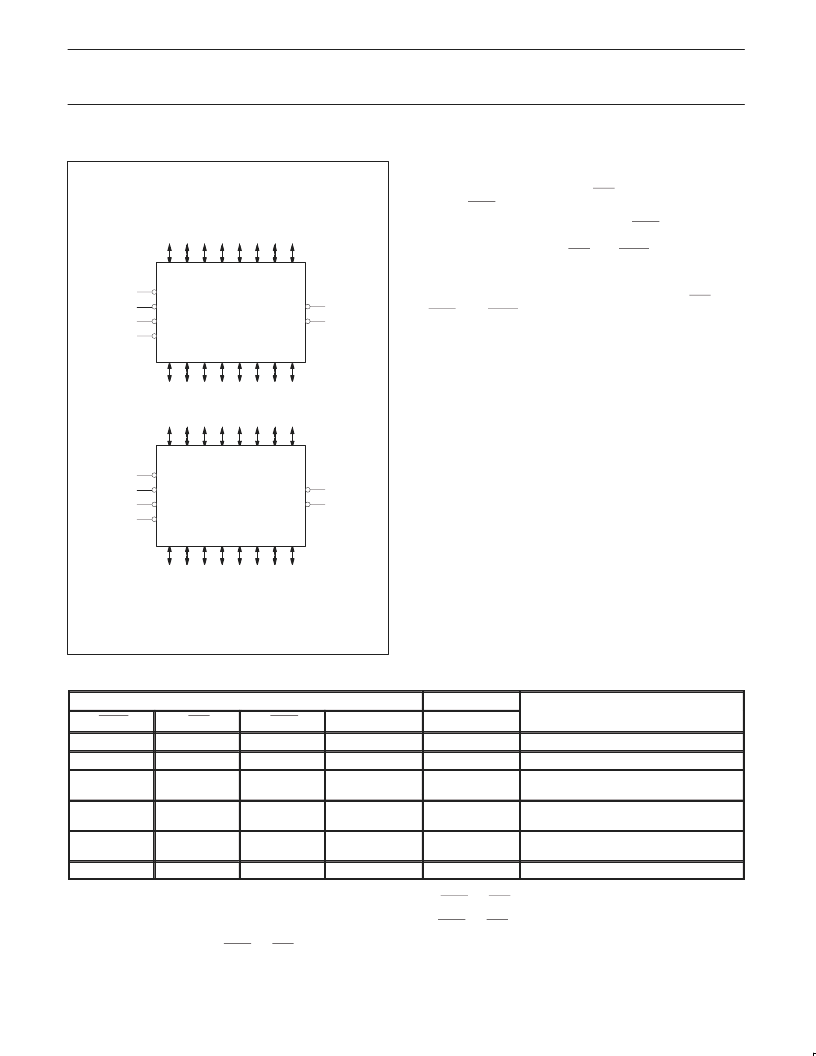

LOGIC SYMBOL

3

54

1EAB

1EBA

2

1LEAB

55

1LEBA

1

1OEAB

56

1OEBA

26

31

2EAB

2EBA

27

2LEAB

30

2LEBA

28

2OEAB

29

2OEBA

5

6

10

12

13

14

8

9

52

51

47

45

44

43

49

48

15

16

20

21

23

24

17

19

42

41

37

36

34

33

40

38

SH00038

1A0 1A1 1A2 1A3 1A4 1A5 1A6 1A7

1B0 1B1 1B2 1B3 1B4 1B5 1B6 1B7

2A0 2A1 2A2 2A3 2A4 2A5 2A6 2A7

2B0 2B1 2B2 2B3 2B4 2B5 2B6 2B7

FUNCTIONAL DESCRIPTION

The 74ABT16543 contains two sets of eight D-type latches, with

separate control pins for each set. Using data flow from A to B as an

example, when the A-to-B Enable (nEAB) input and the A-to-B Latch

Enable (nLEAB) input are Low the A-to-B path is transparent.

A subsequent Low-to-High transition of the nLEAB signal puts the A

data into the latches where it is stored and the B outputs no longer

change with the A inputs. With EAB and nOEAB both Low, the

3-State B output buffers are active and display the data present at

the outputs of the A latches.

Control of data flow from B to A is similar, but using the nEBA,

nLEBA, and nOEBA inputs.

FUNCTION TABLE

INPUTS

OUTPUTS

STATUS

nOEXX

nEXX

nLEXX

nAx or nBx

nBx or nAx

H

X

X

X

Z

Disabled

X

H

X

X

Z

Disabled

L

L

↑

↑

L

L

L

L

h

l

Z

Z

Disabled + Latch

L

L

↑

↑

h

l

H

L

Latch + Display

L

L

L

L

L

L

H

L

H

L

Transparent

L

L

H

X

NC

Hold

H =

h

L

l

X =

↑

=

NC=

Z =

High voltage level

High voltage level one set-up time prior to the Low-to-High transition of nLEXX or nEXX (XX = AB or BA)

Low voltage level

Low voltage level one set-up time prior to the Low-to-High transition of nLEXX or nEXX (XX = AB or BA)

Don’t care

Low-to-High transition of nLEXX or nEXX (XX = AB or BA)

No change

High impedance or “off” state

=

=

=

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74ABTH16543DL | 16-bit latched transceivers with dual enable 3-State |

| 74ABT16543 | 16-Bit Registered Transceiver with 3-STATE Outputs |

| 74ABT16543CMTD | 16-Bit Registered Transceiver with 3-STATE Outputs |

| 74ABT16543CSSC | 16-Bit Registered Transceiver with 3-STATE Outputs |

| 74ABT16543CMTDX | 16-Bit Registered Transceiver with 3-STATE Outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74ABT16543DL-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dual 8-bit Bus Transceiver |

| 74ABT16600DGGRE4 | 功能描述:總線收發(fā)器 18-Bit Univ Bus Trncvr W/3-St Otpt RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74ABT16600DGGRG4 | 功能描述:總線收發(fā)器 18B Uni Bus Xceivers RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74ABT16601DGGRE4 | 功能描述:通用總線函數(shù) 18-Bit Univ Bus Trncvr W/3-St Otpt RoHS:否 制造商:Texas Instruments 邏輯類型:CMOS 邏輯系列:74VMEH 電路數(shù)量:1 開啟電阻(最大值): 傳播延遲時間:10.1 ns 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大工作溫度:+ 85 C 最小工作溫度:0 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74ABT16601DGGRG4 | 功能描述:通用總線函數(shù) 18B Uni Bus Xceivers RoHS:否 制造商:Texas Instruments 邏輯類型:CMOS 邏輯系列:74VMEH 電路數(shù)量:1 開啟電阻(最大值): 傳播延遲時間:10.1 ns 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大工作溫度:+ 85 C 最小工作溫度:0 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。