- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369299 > 74ACT573PC (FAIRCHILD SEMICONDUCTOR CORP) Two 1-Bit LVTTL/GTLP Adj-Edge-Rate Bus Xcvrs w Split LVTTL Port, Fdbk Path and Selectable Polarity 20-TSSOP -40 to 85 PDF資料下載

參數(shù)資料

| 型號: | 74ACT573PC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Two 1-Bit LVTTL/GTLP Adj-Edge-Rate Bus Xcvrs w Split LVTTL Port, Fdbk Path and Selectable Polarity 20-TSSOP -40 to 85 |

| 中文描述: | ACT SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDIP20 |

| 封裝: | 0.300 INCH, PLASTIC, MS-001, DIP-20 |

| 文件頁數(shù): | 1/11頁 |

| 文件大小: | 244K |

| 代理商: | 74ACT573PC |

1/11

April 2001

I

HIGH SPEED: t

PD

= 5ns (TYP.) at V

CC

= 5V

LOW POWER DISSIPATION:

I

CC

= 4

μ

A(MAX.) at T

A

=25°C

COMPATIBLE WITH TTL OUTPUTS

V

IH

= 2V (MIN.), V

IL

= 0.8V (MAX.)

50

TRANSMISSION LINE DRIVING

CAPABILITY

SYMMETRICAL OUTPUT IMPEDANCE:

|I

OH

| = I

OL

= 24mA (MIN)

BALANCED PROPAGATION DELAYS:

t

PLH

t

PHL

OPERATING VOLTAGE RANGE:

V

CC

(OPR) = 4.5V to 5.5V

PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 573

IMPROVED LATCH-UP IMMUNITY

I

I

I

I

I

I

I

I

DESCRIPTION

The 74ACT573 is an advanced high-speed CMOS

OCTAL D-TYPE LATCH with 3 STATE OUTPUT

NON INVERTING fabricated with sub-micron

silicon gate and double-layer metal wiring C

2

MOS

technology.

These 8 bit D-Type latch are controlled by a latch

enable input (LE) and an output enable input (OE).

While the LE inputs is held at a high level, the Q

outputs will follow the data input .

When the LE is taken low, the Q outputs will be

latched precisely or inversely at the logic level of D

input data. While the (OE) input is low, the 8

outputs will be in a normal logic state (high or low

logic level) and while high level the outputs will be

in a high impedance state.

This device is designed to interface directly High

Speed CMOS systems with TTL and NMOS

components.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them 2KV ESD immunity and transient excess

voltage.

74ACT573

OCTAL D-TYPE LATCH

WITH 3 STATE OUTPUTS (NON INVERTED)

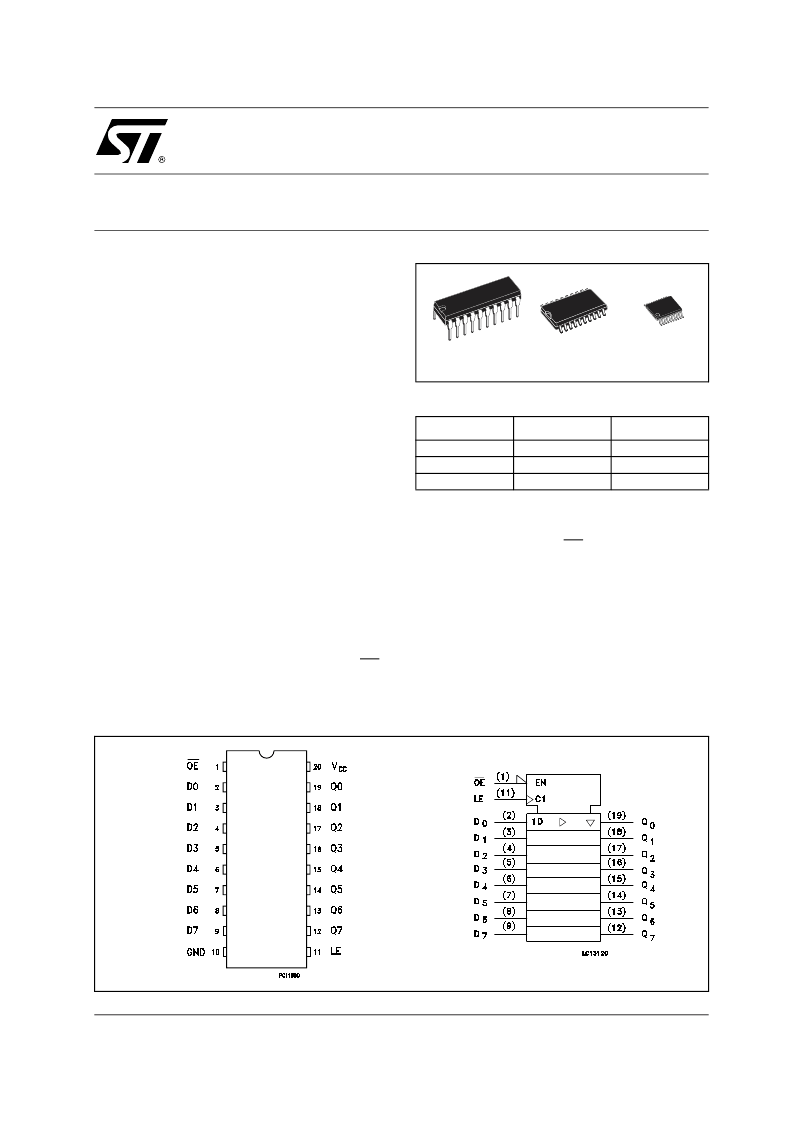

PIN CONNECTION AND IEC LOGIC SYMBOLS

ORDER CODES

PACKAGE

TUBE

T & R

DIP

SOP

TSSOP

74ACT573B

74ACT573M

74ACT573MTR

74ACT573TTR

TSSOP

DIP

SOP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74ACT573SJ | Two 1-Bit LVTTL/GTLP Adj-Edge-Rate Bus Xcvrs w Split LVTTL Port, Fdbk Path and Selectable Polarity 20-TSSOP -40 to 85 |

| 74ACT573SC | Octal Latch with 3-STATE Outputs |

| 74ACT574 | Octal D-Type Flip Flop with 3 State Output Non Inverting(三態(tài)輸出八D觸發(fā)器) |

| 74ACT74B | 8-Bit LVTTL-GTLP Adjustable-Edge-Rate Registered Transceiver with Split LVTTL Port and Feedback Path 56-BGA MICROSTAR JUNIOR -40 to 85 |

| 74ACT74M | DUAL D-TYPE FLIP FLOP WITH PRESET AND CLEAR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74ACT573PC | 制造商:Fairchild Semiconductor Corporation 功能描述:74ACT CMOS 74ACT573 DIP20 5.5V |

| 74ACT573PC_Q | 功能描述:閉鎖 Octal Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74ACT573SC | 功能描述:閉鎖 Octal Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74ACT573SC_Q | 功能描述:閉鎖 Octal Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74ACT573SCX | 功能描述:閉鎖 Octal Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。