- 您現在的位置:買賣IC網 > PDF目錄369302 > 74F163ASC (FAIRCHILD SEMICONDUCTOR CORP) Synchronous Presettable Binary Counter PDF資料下載

參數資料

| 型號: | 74F163ASC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Synchronous Presettable Binary Counter |

| 中文描述: | F/FAST SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT UP BINARY COUNTER, PDSO16 |

| 封裝: | 0.150 INCH, MS-012, SOIC-16 |

| 文件頁數: | 3/10頁 |

| 文件大?。?/td> | 197K |

| 代理商: | 74F163ASC |

Functional Description

The ’F161A and ’F163A count in modulo-16 binary se-

quence. From state 15 (HHHH) they increment to state 0

(LLLL). The clock inputs of all flip-flops are driven in parallel

through a clock buffer. Thus all changes of the Q outputs

(except due to Master Reset of the ’F161A) occur as a re-

sult of, and synchronous with, the LOW-to-HIGH transition

of the CP input signal. The circuits have four fundamental

modes of operation, in order of precedence: asynchronous

reset (’F161A), synchronous reset (’F163A), parallel load,

count-up and hold. Five control inputsDMaster Reset (MR,

’F161A), Synchronous Reset (SR, ’F163A), Parallel Enable

(PE), Count Enable Parallel (CEP) and Count Enable Trickle

(CET)Ddetermine the mode of operation, as shown in the

Mode Select Table. A LOW signal on MR overrides all other

inputs and asynchronously forces all outputs LOW. A LOW

signal on SR overrides counting and parallel loading and

allows all outputs to go LOW on the next rising edge of CP.

A LOW signal on PE overrides counting and allows informa-

tion on the Parallel Data (P

n

) inputs to be loaded into the

flip-flops on the next rising edge of CP. With PE and MR

(’F161A) or SR (’F163A) HIGH, CEP and CET permit count-

ing when both are HIGH. Conversely, a LOW signal on ei-

ther CEP or CET inhibits counting.

The ’F161A and ’F163A use D-type edge triggered flip-flops

and changing the SR, PE, CEP and CET inputs when the CP

is in either state does not cause errors, provided that the

recommended setup and hold times, with respect to the ris-

ing edge of CP, are observed.

The Terminal Count (TC) output is HIGH when CET is HIGH

and the counter is in state 15. To implement synchronous

multi-stage counters, the TC outputs can be used with the

CEP and CET inputs in two different ways. Please refer to

the ’F568 data sheet. The TC output is subject to decoding

spikes due to internal race conditions and is therefore not

recommended for use as a clock or asynchronous reset for

flip-flops, counters or registers.

Logic Equations: Count Enable

e

CEP

#

CET

#

PE

TC

e

Q

0

#

Q

1

#

Q

2

#

Q

3

#

CET

Mode Select Table

*

SR

PE

CET

CEP

Action on the Rising

Clock Edge (

L

)

L

H

H

H

H

X

L

H

H

H

X

X

H

L

X

X

X

H

X

L

Reset (Clear)

Load (P

n

Q

n

)

Count (Increment)

No Change (Hold)

No Change (Hold)

*

For ’F163A only

H

e

HIGH Voltage Level

L

e

LOW Voltage Level

X

e

Immaterial

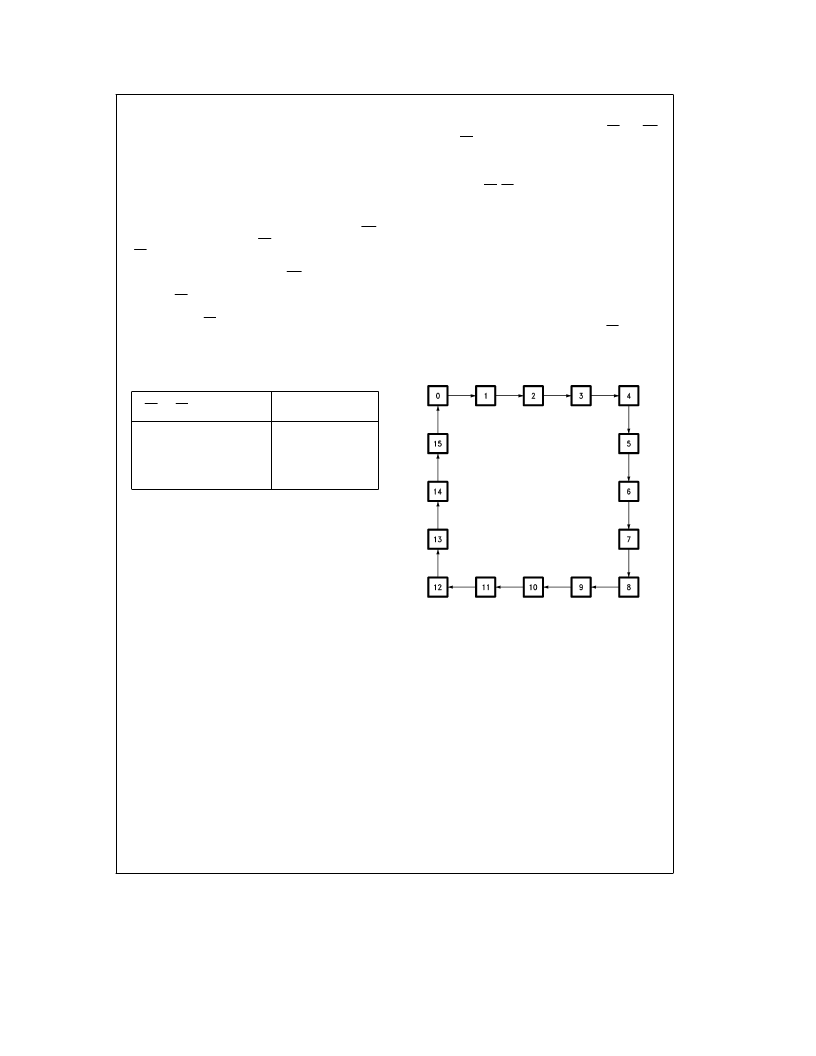

State Diagram

TL/F/9486–5

3

相關PDF資料 |

PDF描述 |

|---|---|

| 74F163ASJ | Synchronous Presettable Binary Counter |

| 74F164A | Serial-In, Parallel-Out Shift Register(串進并出移位寄存器) |

| 74F181 | 4-Bit Arithmetic Logic Unit(4位算術邏輯單元) |

| 74F189 | 64-Bit Random Access Memory with TRI-STATE Outputs(帶三態(tài)輸出的64位RAM) |

| 74F190 | Up/Down Decade Counter with Preset and Ripple Clock(帶可預置和脈動時鐘的可逆十進制計數器) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 74F163ASC_Q | 功能描述:計數器 IC Syn 4-Bit Binary Ctr RoHS:否 制造商:NXP Semiconductors 計數器類型:Binary Counters 邏輯系列:74LV 位數:10 計數法: 計數順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

| 74F163ASCQR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Synchronous Up Counter |

| 74F163ASCX | 功能描述:計數器移位寄存器 Syn 4-Bit Binary Ctr RoHS:否 制造商:Texas Instruments 計數器類型: 計數順序:Serial to Serial/Parallel 電路數量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| 74F163ASJ | 功能描述:計數器移位寄存器 Syn 4-Bit Binary Ctr RoHS:否 制造商:Texas Instruments 計數器類型: 計數順序:Serial to Serial/Parallel 電路數量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| 74F163ASJ_Q | 功能描述:計數器 IC Syn 4-Bit Binary Ctr RoHS:否 制造商:NXP Semiconductors 計數器類型:Binary Counters 邏輯系列:74LV 位數:10 計數法: 計數順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。