- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360460 > 74HC4059 (NXP Semiconductors N.V.) Programmable divide-by-n counter PDF資料下載

參數(shù)資料

| 型號: | 74HC4059 |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 通用總線功能 |

| 英文描述: | Programmable divide-by-n counter |

| 中文描述: | 可編程分頻氮計數(shù)器 |

| 文件頁數(shù): | 12/20頁 |

| 文件大小: | 147K |

| 代理商: | 74HC4059 |

1998 Jul 08

12

Philips Semiconductors

Product specification

Programmable divide-by-n counter

74HC/HCT4059

APPLICATION INFORMATION

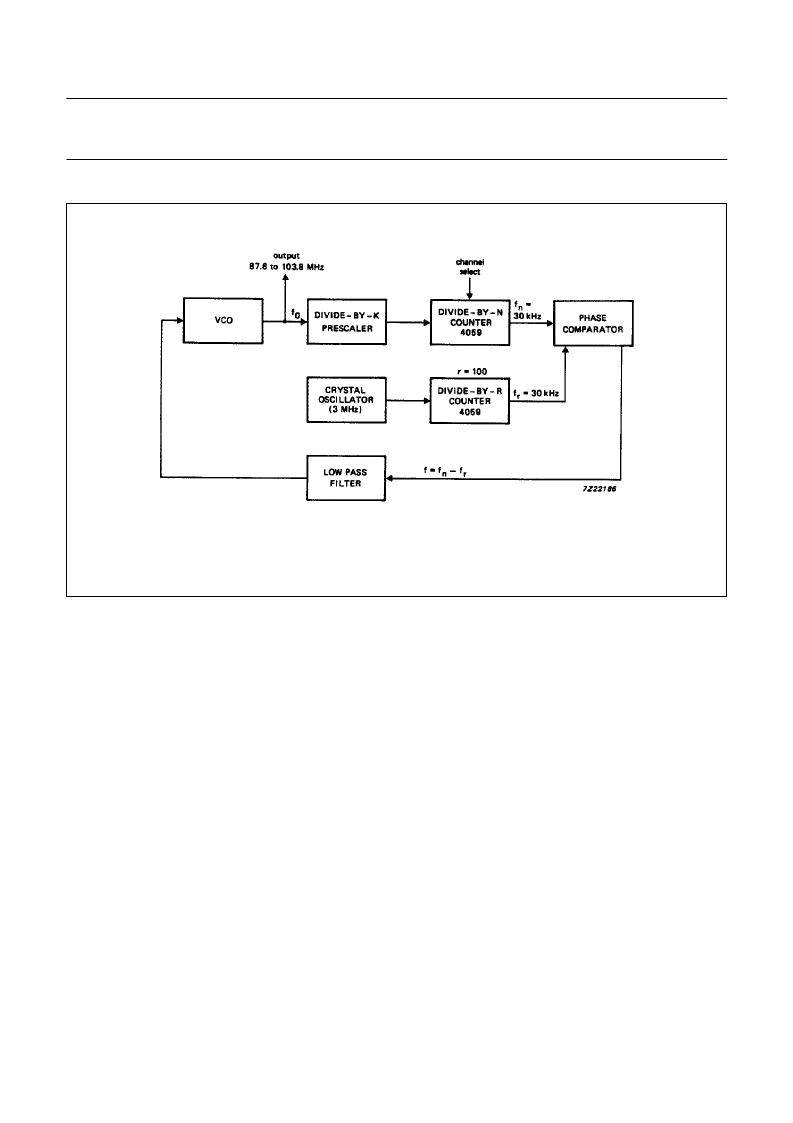

Fig.10 Example showing the application of the PC74HC/HCT4059 in a phase-locked-loop (PLL) for a FM band

synthesizer.

Calculating the minimum and maximum divide-by-n

values:

Output frequency range = 87.6 to 103.8 MHz

(CCIR band 2)

Channel spacing frequency (f

c

) = 300 kHz

Division factor prescaler (k) = 10

Reference frequency (f

r

) =

Maximum divide-by-n value =

Minimum divide-by-n value =

Fixed divide-by-n value =

Application of the “4059” as divide-by-n counter allows

programming of the channel spacing (shown in equations

as 300 kHz). A channel in the CCIR band 2 is selected by

the divide-by-n counter as follows:

channel = n

290

f

c

k

10

30 kHz

=

=

300 kHz

103.8 MHz

346

=

300 kHz

87.6 MHz

292

=

30 kHz

100

=

Figure 11 shows a BCD switch compatible arrangement

suitable for divide-by-5 and divide-by-8 modes, which can

be adapted (with minimal changes) to the other

divide-by-modes. In order to be able to preset to any

number from 3 to 256 000, while preserving the BCD

switch compatible character of the JAM inputs, a rather

complex cascading scheme is necessary because the

“4059” can never be preset to count less than 3. Logic

circuitry is required to detect a condition where one of the

numbers to be preset in the “4059” is

<

3. In order to

simplify the detection logic, only that condition is detected

where the JAM inputs to terminals 6, 7 and 9 would be

LOW during one count. If such a condition is detected, and

if at least 1 is expected to be jammed into the MSB

counter, the detection logic removes one from the number

to be jammed into the MSB counter (with a place value of

2 000 times the divide-by-mode) and jams the same 2 000

into the “4059” by forcing pins 6, 7 and 9 HIGH.

The general circuit in Fig.11 can be simplified considerably

if the range of the cascaded counters do not start at a very

low value.

Figure 12 shows an arrangement in the divide-by-4 mode,

where the counting range extends in a BCD switch

compatible manner from 99 003 to 114 999.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74HC4060 | 14-stage binary ripple counter with oscillator |

| 74HC4067 | 16-channel analog multiplexer/demultiplexer |

| 74HCT4067 | 16-channel analog multiplexer/demultiplexer |

| 74HC4075 | Triple 3-input OR gate |

| 74HCT4075 | Triple 3-input OR gate |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74HC4059D | 功能描述:計數(shù)器 IC PROGRMBL DIVIDE-BY-N COUNTER RoHS:否 制造商:NXP Semiconductors 計數(shù)器類型:Binary Counters 邏輯系列:74LV 位數(shù):10 計數(shù)法: 計數(shù)順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

| 74HC4059D,112 | 功能描述:計數(shù)器 IC PROGRMBL DIVIDE-BY-N RoHS:否 制造商:NXP Semiconductors 計數(shù)器類型:Binary Counters 邏輯系列:74LV 位數(shù):10 計數(shù)法: 計數(shù)順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

| 74HC4059D,118 | 功能描述:計數(shù)器移位寄存器 PROGRMBL DIVIDE-BY-N RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| 74HC4059D112 | 制造商:Rochester Electronics LLC 功能描述: 制造商:NXP 功能描述: 制造商:NXP Semiconductors 功能描述: |

| 74HC4059DB | 功能描述:計數(shù)器 IC PROGRMBL DIVIDE-BY-N COUNTER RoHS:否 制造商:NXP Semiconductors 計數(shù)器類型:Binary Counters 邏輯系列:74LV 位數(shù):10 計數(shù)法: 計數(shù)順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。