- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369314 > 74LS194A (National Semiconductor Corporation) 4-Bit Bidirectional Universal Shift Register PDF資料下載

參數(shù)資料

| 型號(hào): | 74LS194A |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | 4-Bit Bidirectional Universal Shift Register |

| 中文描述: | 4位雙向通用移位寄存器 |

| 文件頁(yè)數(shù): | 1/8頁(yè) |

| 文件大?。?/td> | 166K |

| 代理商: | 74LS194A |

TL/F/6407

5

June 1989

54LS194A/DM74LS194A 4-Bit

Bidirectional Universal Shift Register

General Description

This bidirectional shift register is designed to incorporate

virtually all of the features a system designer may want in a

shift register; they feature parallel inputs, parallel outputs,

right-shift and left-shift serial inputs, operating-mode-control

inputs, and a direct overriding clear line. The register has

four distinct modes of operation, namely:

Parallel (broadside) load

Shift right (in the direction Q

A

toward Q

D

)

Shift left (in the direction Q

D

toward Q

A

)

Inhibit clock (do nothing)

Synchronous parallel loading is accomplished by applying

the four bits of data and taking both mode control inputs, S0

and S1, high. The data is loaded into the associated flip-

flops and appear at the outputs after the positive transition

of the clock input. During loading, serial data flow is inhibit-

ed.

Shift right is accomplished synchronously with the rising

edge of the clock pulse when S0 is high and S1 is low.

Serial data for this mode is entered at the shift-right data

input. When S0 is low and S1 is high, data shifts left syn-

chronously and new data is entered at the shift-left serial

input.

Clocking of the flip-flop is inhibited when both mode control

inputs are low.

Features

Y

Parallel inputs and outputs

Y

Four operating modes:

Synchronous parallel load

Right shift

Left shift

Do nothing

Y

Positive edge-triggered clocking

Y

Direct overriding clear

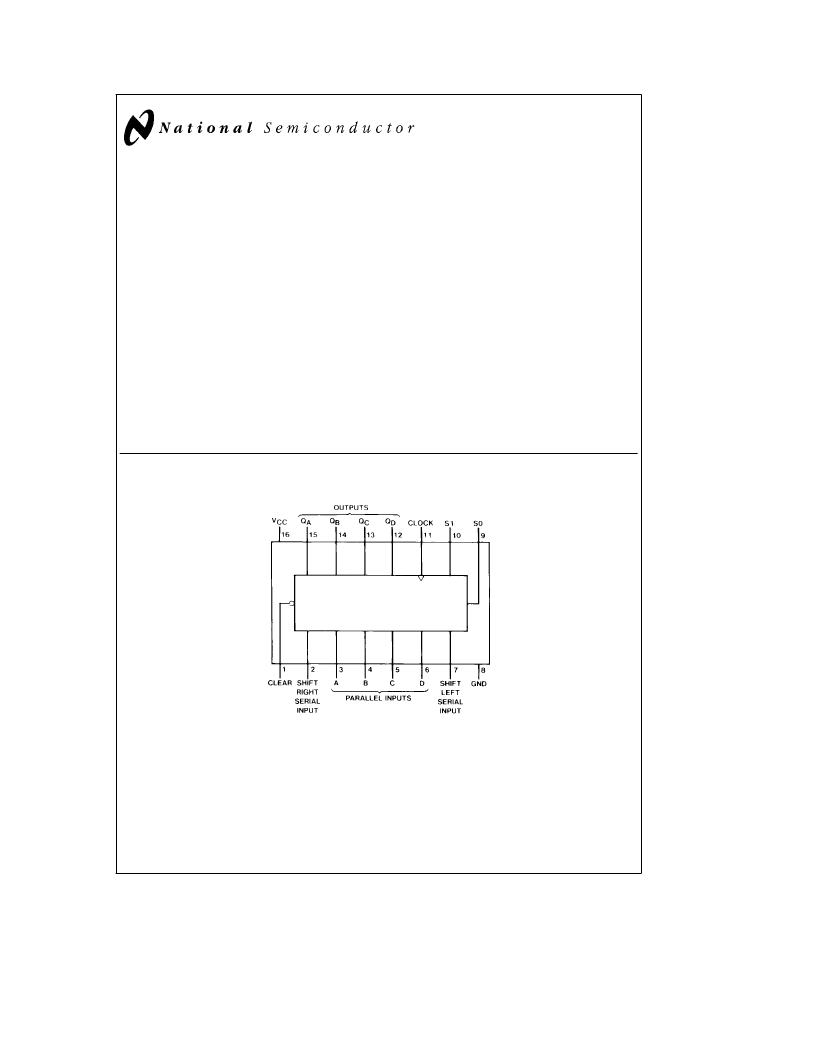

Connection Diagram

Dual-In-Line Package

TL/F/6407–1

Order Number 54LS194ADMQB, 54LS194AFMQB,

54LS194ALMQB, DM74LS194AM or DM74LS194AN

See NS Package Number E20A, J16A, M16A, N16E or W16A

C

1995 National Semiconductor Corporation

RRD-B30M105/Printed in U. S. A.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74LS195 | 4-bit Parallel-Access Shift Registers |

| 74LS195 | 4-BIT PARALLEL-ACCESS SHIFT REGISTERS |

| 74LS195 | LOW POWER SCHOTTKY |

| 74LS195 | UNIVERSAL 4-BIT SHIFT REGISTER |

| 74LS196 | 50/30/100-MHz [RESETTABLE DECADE OR BINARY COUNTERS/LATCHES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74LS194ADC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 74LS194AN | 制造商:NXP Semiconductors 功能描述:Shift Register, 16 Pin, Plastic, DIP 制造商:Texas Instruments 功能描述:Shift Register, 16 Pin, Plastic, DIP |

| 74LS194APC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 74LS194DC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 74LS194PC | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。