- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360487 > 74LV27PW (NXP SEMICONDUCTORS) Triple 3-input NOR gate PDF資料下載

參數(shù)資料

| 型號(hào): | 74LV27PW |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | Triple 3-input NOR gate |

| 中文描述: | LV/LV-A/LVX/H SERIES, TRIPLE 3-INPUT NOR GATE, PDSO14 |

| 封裝: | 4.40 MM, PLASTIC, SOT-402-1, TSSOP-14 |

| 文件頁(yè)數(shù): | 3/10頁(yè) |

| 文件大小: | 114K |

| 代理商: | 74LV27PW |

Philips Semiconductors

Product specification

74LV27

Triple 3-input NOR gate

1998 Apr 20

3

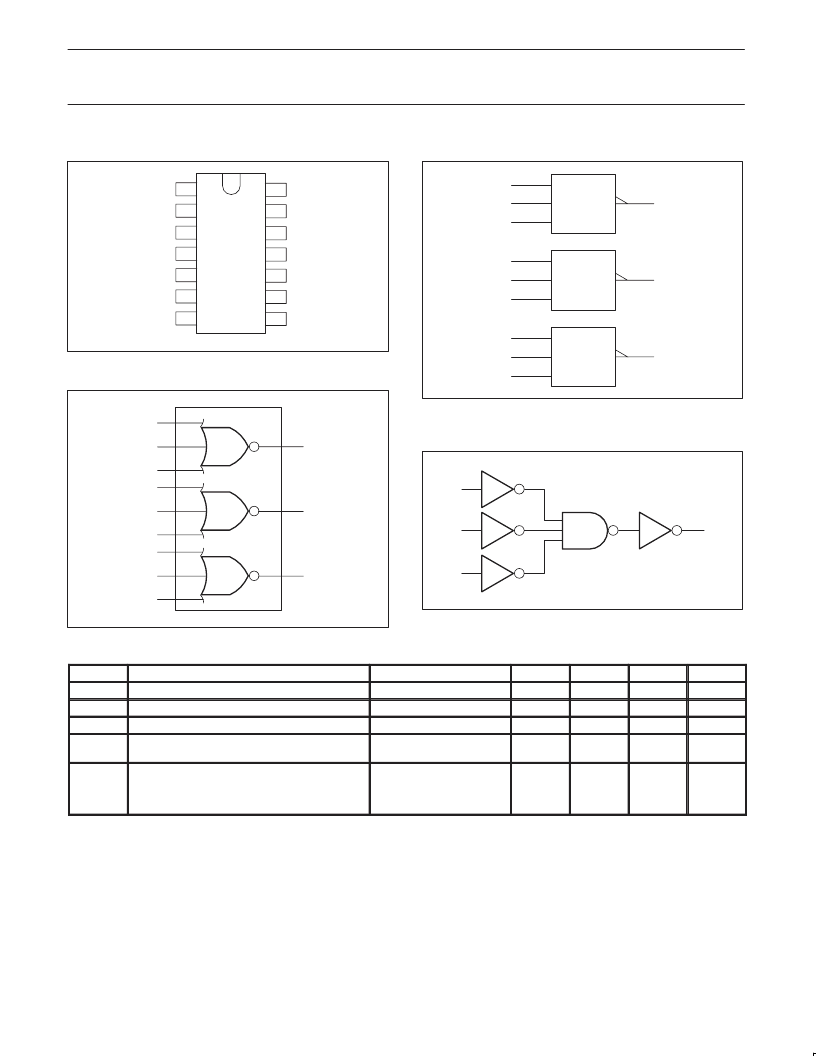

PIN CONFIGURATION

1

2

3

4

5

6

7

1A

1B

2A

2B

2C

2Y

GND

VCC

1C

1Y

3C

3B

3A

3Y

14

13

12

11

10

9

8

SV00446

LOGIC SYMBOL

2C

2A

2Y

5

3

6

2B

4

3C

3A

3Y

11

9

8

3B

10

1C

1A

1Y

13

1

12

1B

2

SV00447

LOGIC SYMBOL (IEEE/IEC)

2

4

10

1

3

9

13

5

11

12

6

8

SV00448

≥

1

≥

1

≥

1

LOGIC DIAGRAM

A

C

Y

B

SV00449

RECOMMENDED OPERATING CONDITIONS

SYMBOL

V

CC

DC supply voltage

V

I

Input voltage

V

O

Output voltage

PARAMETER

CONDITIONS

See Note 1

MIN

1.0

0

0

–40

–40

–

–

–

–

TYP

3.3

–

–

MAX

5.5

V

CC

V

CC

+85

+125

500

200

100

50

UNIT

V

V

V

T

amb

Operating ambient temperature range in free air

See DC and AC

characteristics

V

CC

= 1.0V to 2.0V

V

CC

= 2.0V to 2.7V

V

CC

= 2.7V to 3.6V

V

CC

= 3.6V to 5.5V

°

C

t

r

, t

f

Input rise and fall times

–

–

–

–

ns/V

NOTE:

1. The LV is guaranteed to function down to V

CC

= 1.0V (input levels GND or V

CC

); DC characteristics are guaranteed from V

CC

= 1.2V to V

CC

= 5.5V.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74LV27PWDH | Triple 3-input NOR gate |

| 74LV27N | Triple 3-input NOR gate |

| 74LV30D | 2K, 256 X 8 SERIAL EE, 1.8V IND, -40C to +85C, 8-TSSOP, TUBE |

| 74LV30DB | 2K, 256 X8 SERIAL EE, 1.8V, -40C to +85C, 8-DFN, T/R |

| 74LV30N | Single 8-input NAND Gate |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74LV27PWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Triple 3-input NOR gate |

| 74LV27PW-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Triple 3-input NOR Gate |

| 74LV2G126AUSE-E | 制造商:Renesas Electronics Corporation 功能描述:Cut Tape |

| 74LV2G14AUSE-E | 制造商:Renesas Electronics 功能描述:Cut Tape 制造商:Renesas 功能描述:Inverter Schmitt Trigger 3-Element CMOS 8-Pin SSOP T/R |

| 74LV2G34AUSE-E | 制造商:Renesas Electronics Corporation 功能描述:Buffer 3-CH Non-Inverting CMOS 8-Pin SSOP T/R Cut Tape |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。