- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360546 > 7AHCT273PWDH (NXP SEMICONDUCTORS) Marine Lamp, 4 in x 6 in [101,6 mm x 152,4 mm], Wide Flood Beam Pattern, 12 Vdc/50 W/4 A, Stud mounting PDF資料下載

參數(shù)資料

| 型號: | 7AHCT273PWDH |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | Marine Lamp, 4 in x 6 in [101,6 mm x 152,4 mm], Wide Flood Beam Pattern, 12 Vdc/50 W/4 A, Stud mounting |

| 中文描述: | AHCT/VHCT SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO20 |

| 封裝: | 4.40 MM, PLASTIC, SOT-360-1, TSSOP-20 |

| 文件頁數(shù): | 2/20頁 |

| 文件大?。?/td> | 92K |

| 代理商: | 7AHCT273PWDH |

1999 Sep 01

2

Philips Semiconductors

Product specification

Octal D-type flip-flop with reset;

positive-edge trigger

74AHC273; 74AHCT273

FEATURES

Ideal buffer for MOS microcontroller or memory

Common clock and master reset

ESD protection:

HBM EIA/JESD22-A114-A exceeds 2000 V

MM EIA/JESD22-A115-A exceeds 200 V

CDM EIA/JESD22-C101 exceeds 1000 V

Balanced propagation delays

All inputs have Schmitt trigger actions

Inputs accepts voltages higher than V

CC

See ‘377’ for clock enable version

See ‘373’ for transparent latch version

See ‘374’ for 3-state version

For AHC only: operates with CMOS input levels

For AHCT only: operates with TTL input levels

Specified from

40 to +85

°

C and

40 to +125

°

C.

DESCRIPTION

The 74AHC/AHCT273 are high-speed Si-gate CMOS

devices and are pin compatible with low power Schottky

TTL (LSTTL). They are specified in compliance with

JEDEC standard no. 7A.

The 74AHC/AHCT273 have eight edge-triggered, D-type

flip-flops with individual D inputs and Q outputs.

Thecommonclock(CP)andmasterreset(MR)inputsload

and reset (clear) all flip-flops simultaneously.

The state of each D input, one set-up time before the

LOW-to-HIGH clock transition, is transferred to the

corresponding output (Q

n

) of the flip-flop.

All outputs will be forced LOW independently of clock or

data inputs by a LOW on the MR input.

The device is useful for applications where the true output

only is required and the clock and master reset are

common to all storage elements.

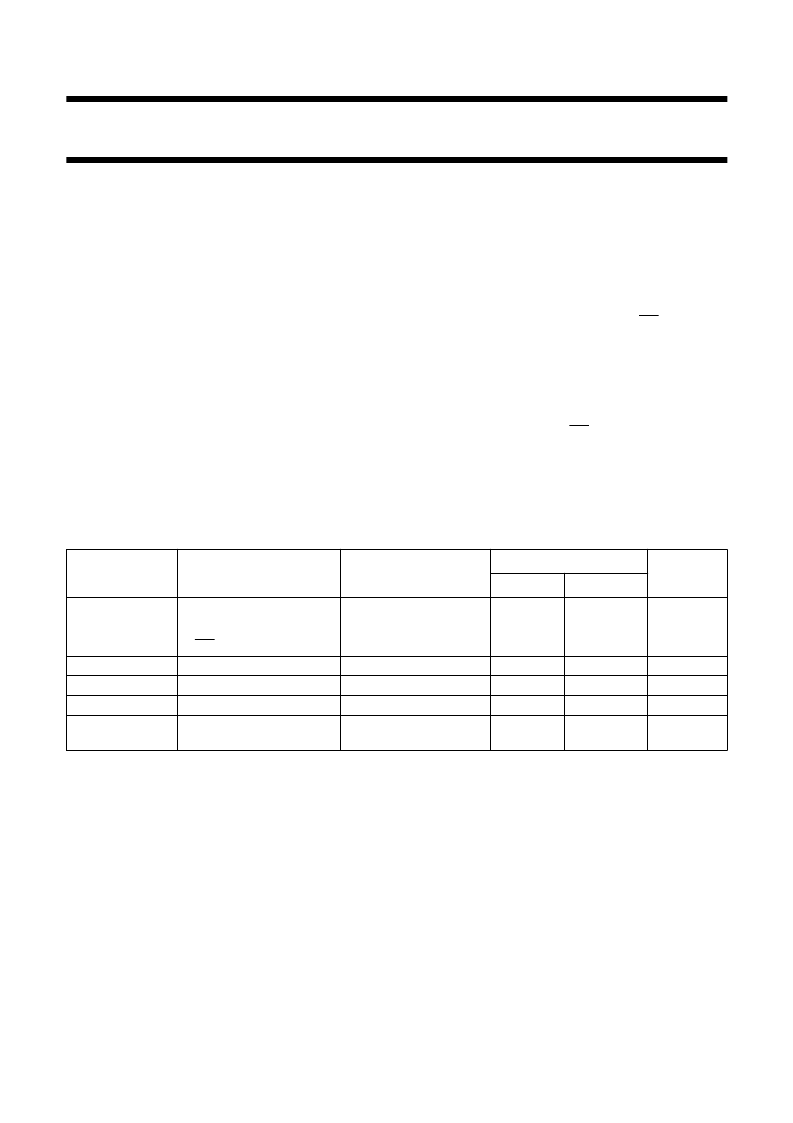

QUICK REFERENCE DATA

Ground = 0 V; T

amb

= 25

°

C; t

r

= t

f

≤

3.0 ns.

Notes

1.

C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W).

P

D

= C

PD

×

V

CC2

×

f

i

+

∑

(C

L

×

V

CC2

×

f

o

) where:

f

i

= input frequency in MHz;

f

o

= output frequency in MHz;

∑

(C

L

×

V

CC2

×

f

o

) = sum of outputs;

C

L

= output load capacitance in pF;

V

CC

= supply voltage in Volts.

The condition is V

I

= GND to V

CC

.

2.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

AHC

AHCT

t

PHL

/t

PLH

propagation delay

CP to Q

n

MR to Q

n

maximum clock frequency

input capacitance

output capacitance

power dissipation

capacitance

C

L

= 15 pF; V

CC

= 5 V

4.2

3.7

120

3.0

4.0

14.0

4.0

3.9

120

3.0

4.0

18.0

ns

ns

MHz

pF

pF

pF

f

max

C

I

C

O

C

PD

C

L

= 15 pF; V

CC

= 5 V

V

I

= V

CC

or GND

C

L

= 50 pF; f = 1 MHz;

notes 1 and 2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 7AHCT373PWDH | Replacement Sealed Beams, 4 in x 6 in [101,6 mm x 152,4 mm], Trapezoid Beam Pattern, 12 Vdc/50 W/4 A |

| 7AHCT374PWDH | Octal D-type flip-flop; positive edge-trigger; 3-state |

| 7AHCT541PWDH | Octal buffer/line driver; 3-state |

| 7AHCT573PWDH | Replacement Sealed Beams, 4 in x 6 in [101,6 mm x 152,4 mm], Spot Beam Pattern, 24 Vdc/60 W/2.5 A |

| 7C33128PFS36A | 3.3V 128K x 32/36 pipeline burst synchronous SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 7AHCT373PWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal D-type transparent latch; 3-state |

| 7AHCT374PWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal D-type flip-flop; positive edge-trigger; 3-state |

| 7AHCT541PWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal buffer/line driver; 3-state |

| 7AHCT573PWDH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal D-type transparent latch; 3-state |

| 7AM027A5-1079-5 | 制造商:Klixon 功能描述:THERMAL PROTECTOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。