- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376469 > 818H8E (Electronic Theatre Controls, Inc.) 2 X 4 8-Pole Filters PDF資料下載

參數(shù)資料

| 型號: | 818H8E |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 2 X 4 8-Pole Filters |

| 中文描述: | 2 × 4 8極點濾波器 |

| 文件頁數(shù): | 2/13頁 |

| 文件大?。?/td> | 625K |

| 代理商: | 818H8E |

8-Bit Programmable Filters

818 Series

Digital Tuning &

Control Characteristics

25 Locust St, Haverhill, Massachusetts 01830 Tel: 800/252-7074, 978/374-0761 FAX: 978/521-1839

e-mail: sales@freqdev.com Web Address: http://www.freqdev.com

2

MSB

---

---

---

---

---

---

LSB

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

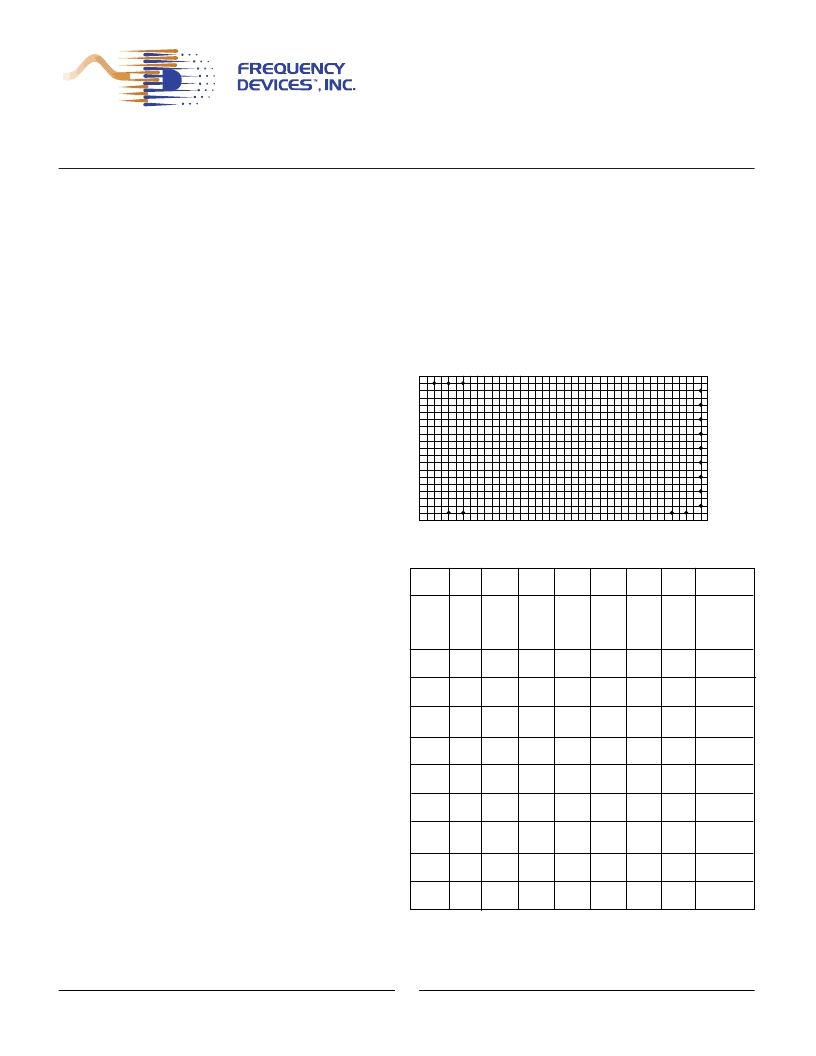

0

0

0

0

0

0

0

0

f

max

/256

0

0

0

0

0

0

0

1

f

max

/128

0

0

0

0

0

0

1

1

f

max

/64

0

0

0

0

0

1

1

1

f

max

/32

0

0

0

0

1

1

1

1

f

max

/16

0

0

0

1

1

1

1

1

f

max

/8

0

0

1

1

1

1

1

1

f

max

/4

0

1

1

1

1

1

1

1

f

max

/2

1

1

1

1

1

1

1

1

fmax

Bit

Weight

fc

Corner

Frequency

+Vs

OUT

-Vs

D

D

D

D

GND

D

D

D

D

C

P

IN

Bottom View

Os/NC

4

5

3

2

1

0

6

7

Pin-Out Key

IN

OUT Analog Output Signal

GND Power and Signal Return

"P"

Transition Polarity Bit

"C"

Tuning Strobe Bit

+Vs

Supply Voltage, Positive

-Vs

Supply Voltage, Negative

Os

Optional Offset Adjustment

NC

No Connect (Highpass Models)

Analog Input Signal

D

7

Tuning Bit 7 (MSB)

D

6

Tuning Bit 6

D

5

Tuning Bit 5

D

4

Tuning Bit 4

D

3

Tuning Bit 3

D

2

Tuning Bit 2

D

1

Tuning Bit 1

D

0

Tuning Bit 0 (LSB)

Digital Tuning Characteristics

The digital tuning interface circuits are two 4042 quad CMOS

latches which accept the following CMOS-compatible inputs:

eight tuning bits (D

0

- D

7

), a latch strobe bit (C), and a transition

polarity bit (P).

Filter tuning follows the tuning equation given below:

f

c

= ( f

max

/256 ) [ 1 + D

7

x 2

2

7

+ D

6

x 2

0

]

6

+ D

5

x 2

5

+ D

4

x 2

4

+ D

3

x

3

+ D

2

x 2

2

+ D

1

x 2

1

+ D

0

x 2

where D

1

- D

7

= "0" or "1", and

f

max

= Maximum tuning frequency;

f

c

= corner frequency;

Minimum tunable frequency = f

max

/256 (D

0

thru D

7

= 0);

Minimum frequency step (Resolution) = f

max

/256

Data Control Specifications

Data Control Lines

Functions

Latch Strobe (C)

Transition Polarity (P)

Data Control Modes

Mode 1

P = 0; C = 0

frequency follows input codes

P = 0; C = 0

frequency latched on rising edge

Mode 2

P = 1; C = 1

frequency follows input codes

P = 1; C = 1

frequency latched on falling edge

Input Data Levels

Input Voltage (Vs = 15 Vdc)

Low Level In

High Level In

Input Current

High Level In

Low Level In

Input Capacitance

Latch Response

Data Set Up Time

Data Hold Time

Strobe Pulse Width

Input Data Format

Positive Logic

(CMOS Logic)

0 Vdc min.

11 Vdc min.

4 Vdc max.

15 Vdc max.

- 10

+10

5 pF typ

-5

μ

A typ.

-5

μ

A typ.

-1 mA max.

+1

μ

A max.

7.5 pF max.

1

25 nS

50 nS

80 nS min.

Frequency Select Bits

Logic "1" = +Vs

Logic "0" = Gnd

(Binary-Coded)

LSB (least significant bit)

MSB (most significant bit)

256 : 1, Binary Weighted

Bit Weighting

D

0

D

7

Frequency Range

Notes:

1.Frequency data must be present before occurrence of strobe edge.

2.Frequency data must be present after occurrence of strobe edge.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 818L8B | 2 X 4 8-Pole Filters |

| 818L8D80 | 2 X 4 8-Pole Filters |

| 818L8E | 2 X 4 8-Pole Filters |

| 818L8L | 2 X 4 8-Pole Filters |

| 8200 | 4700 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 818H8E-1 | 制造商:FREQUENCYDEVICES 制造商全稱:Frequency Devices, Inc. 功能描述:2" x 4" 8-Pole Filters |

| 818H8E-2 | 制造商:FREQUENCYDEVICES 制造商全稱:Frequency Devices, Inc. 功能描述:2" x 4" 8-Pole Filters |

| 818H8E-3 | 制造商:FREQUENCYDEVICES 制造商全稱:Frequency Devices, Inc. 功能描述:2" x 4" 8-Pole Filters |

| 818H8E-4 | 制造商:FREQUENCYDEVICES 制造商全稱:Frequency Devices, Inc. 功能描述:2" x 4" 8-Pole Filters |

| 818H8E-5 | 制造商:FREQUENCYDEVICES 制造商全稱:Frequency Devices, Inc. 功能描述:2" x 4" 8-Pole Filters |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。