- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24766 > 935031340623 (NXP SEMICONDUCTORS) F/FAST SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 PDF資料下載

參數(shù)資料

| 型號: | 935031340623 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 鎖存器 |

| 英文描述: | F/FAST SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 |

| 封裝: | 3.90 MM, PLASTIC, MS-012AB, SOT-108-1, SO-14 |

| 文件頁數(shù): | 10/12頁 |

| 文件大?。?/td> | 105K |

| 代理商: | 935031340623 |

Philips Semiconductors

Product specification

74F50729

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

1990 Sep 14

7

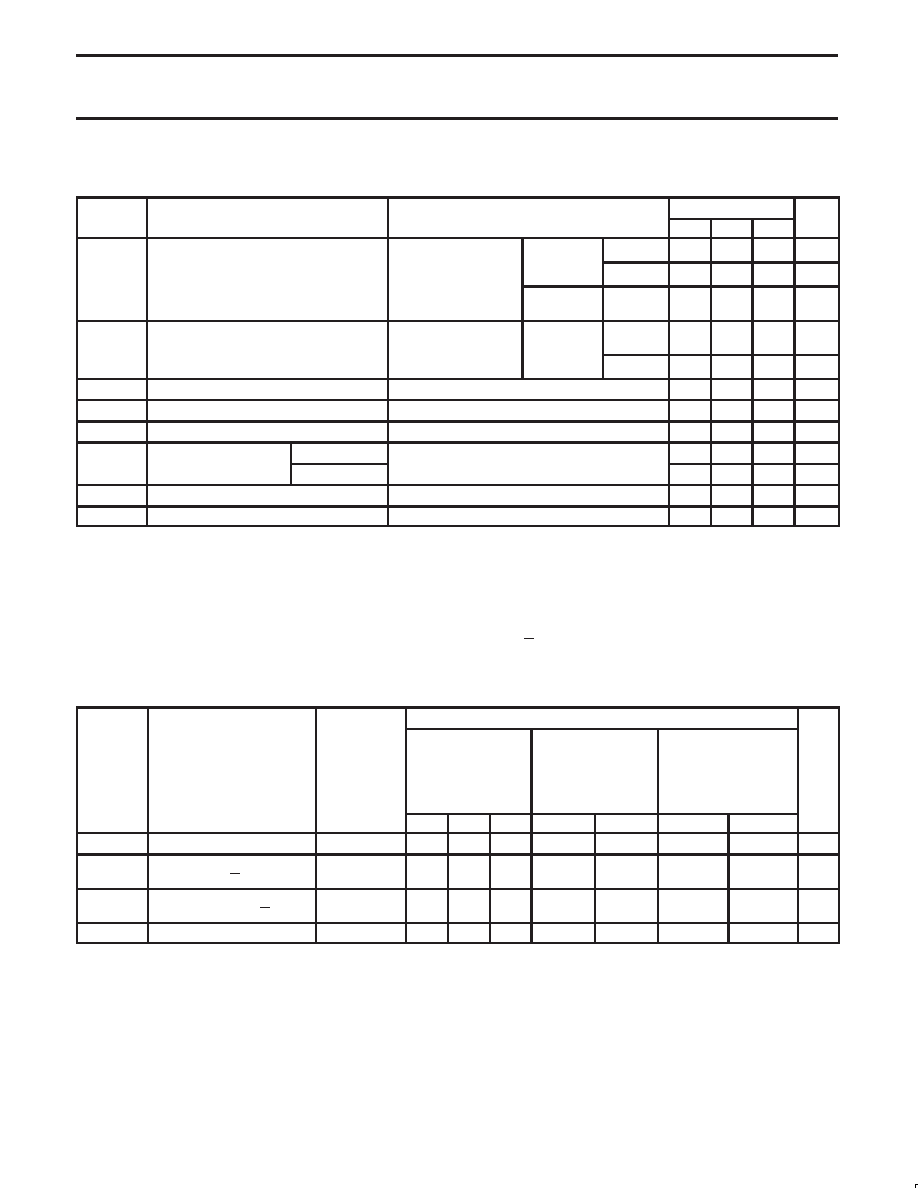

DC ELECTRICAL CHARACTERISTICS

(Over recommended operating free-air temperature range unless otherwise noted.)

SYMBOL

PARAMETER

TEST

LIMITS

UNIT

CONDITIONS1

MIN

TY.2

MAX

VOH

High-level output voltage

VCC = MIN, VIH = MIN

IOH = MAX

±10%V

CC

2.5

V

VIL = MAX,

±5%V

CC

2.7

3.4

V

IOH =

–15mA

±5%V

CC

2.0

V

VOL

Low-level output voltage

VCC = MIN, VIL =

MAX,

IOL = MAX

±10%V

CC

0.30

0.50

V

VIH = MIN

±5%V

CC

0.30

0.50

V

VIK

Input clamp voltage

VCC = MIN, II = IIK

-0.73

-1.2

V

II

Input current at maximum input voltage

VCC = MAX, VI = 7.0V

100

A

IIH

High–level input current

VCC = MAX, VI = 2.7V

20

A

IIL

Low–level input current

Dn

VCC = MAX, VI = 0.5V

-250

A

CPn, SDn, RDn

–20

A

IOS

Short–circuit output current3

VCC = MAX, VO = 2.25V

-60

-150

mA

ICC

Supply current4 (total)

VCC = MAX

19

27

mA

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type

and function table for operating mode.

2. All typical values are at VCC = 5V, Tamb = 25°C.

3. Not more than one output should be shorted at a time. For testing IOS, the use of high-speed test apparatus and/or sample-and-hold

techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting

of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any

sequence of parameter tests, IOS tests should be performed last.

4. Measure ICC with the clock input grounded and all outputs open, then with Q and Q outputs high in turn.

AC ELECTRICAL CHARACTERISTICS

LIMITS

Tamb = +25°C

Tamb = 0°C to

+70

°C

Tamb = –40°C to +85°C

SYMBOL

PARAMETER

TEST

VCC = +5.0V

VCC = +5.0V ± 10%

UNIT

CONDITION

CL = 50pF,

RL = 500

CL = 50pF,

RL = 500

CL = 50pF,

RL = 500

MIN

TYP

MAX

MIN

MAX

MIN

MAX

fmax

Maximum clock frequency

Waveform 1

105

120

85

75

ns

tPLH

tPHL

Propagation delay

CPn to Qn or Qn

Waveform 1

2.0

3.9

6.0

1.5

2.0

6.5

1.5

2.0

7.0

6.5

ns

tPLH

tPHL

Propagation delay

SDn RDn to Qn or Qn

Waveform 2

2.0

3.0

4.0

5.0

6.5

7.5

1.5

2.0

7.5

8.0

1.5

2.0

7.5

8.0

ns

tok(o)

Output skew1, 2

Waveform 4

1.5

ns

NOTES:

1. | tPLH actual –tPHL actual | for any one output compared to any other output where N and M are either LH or HL.

2. Skew lines are valid only under same conditions (temperature, VCC, loading, etc.,).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935031340602 | F/FAST SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 |

| 935008920112 | TELEPHONE MULTIFUNCTION CKT, PDIP8 |

| 935008930112 | TELEPHONE MULTIFUNCTION CKT, PDSO8 |

| 935008930118 | TELEPHONE MULTIFUNCTION CKT, PDSO8 |

| 935008900112 | TELEPHONE MULTIFUNCTION CKT, PDIP14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9350317 | 制造商:Honeywell / Clarostat 功能描述:SST PRESSURE TRANSDUCERS 制造商:Honeywell Sensing and Control 功能描述:SST PRESSURE TRANSDUCERS 制造商:Honeywell Sensing and Control 功能描述:9350317 SST PRESSURE TRANSDUCERS |

| 935032 | 制造商:JWMILLER 功能描述: |

| 9350-3R1 | 制造商:Johanson Manufacturing 功能描述:VARIABLE CAPACITOR |

| 935040870112 | 制造商:NXP Semiconductors 功能描述:IC MIXER FM IF SYSTEM LP 20-SSOP |

| 9350-4R1 | 制造商:Johanson Manufacturing 功能描述:VARIABLE CAPACITOR 制造商:Johanson 功能描述:VARIABLE CAPACITOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。