- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24795 > 935238700118 (NXP SEMICONDUCTORS) LVC/LCX/Z SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 PDF資料下載

參數(shù)資料

| 型號(hào): | 935238700118 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 總線收發(fā)器 |

| 英文描述: | LVC/LCX/Z SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 封裝: | PLASTIC, SOT-370, SSOP-48 |

| 文件頁數(shù): | 5/12頁 |

| 文件大小: | 132K |

| 代理商: | 935238700118 |

Philips Semiconductors

Product specification

74LVC162244A/

74LVCH162244A

16-bit buffer/line driver; with 30

series termination

resistors; 5V input/output tolerant (3-State)

2

1998 Feb 17

853-2014 18975

FEATURES

5 volt tolerant inputs/outputs for interfacing with 5V logic

Wide supply voltage range of 1.2V to 3.6V

Complies with JEDEC standard no. 8-1A

CMOS low power consumption

MULTIBYTETM flow-through standard pin-out architecture

Low inductance multiple power and ground pins for minimum

noise and ground bounce

Direct interface with TTL levels

Bus Hold on data inputs (74LVCH162244A only)

Integrated 30 termination resistors

DESCRIPTION

The 74LVC(H)162244A is a high-performance, low-power,

low-voltage, Si-gate CMOS device, superior to most advanced

CMOS compatible TTL families. Inputs can be driven from either

3.3V or 5V devices. In 3-State operation, outputs can handle 5V.

These features allow the use of these devices in a mixed 3.3V/5V

environment.

The 74LVC(H)162244A is a 16-bit non-inverting buffer/line driver

with 3-State outputs. The device can be used as four 4-bit buffers,

two 8-bit buffers or one 16-bit buffer. The 3-State outputs are

controlled by the output enable inputs 1OE and 2OE. A HIGH on

nOE causes the outputs to assume a high impedance OFF-state.

The 74LVC(H)162244A is designed with 30

series termination

resistors in both HIGH and LOW output stages to reduce line noise.

The device can be used as four 4-bit buffers, two 8-bit buffers or one

16-bit buffer.

The 74LVCH162244A bus hold data inputs eliminates the need for

external pull up resistors to hold unused inputs.

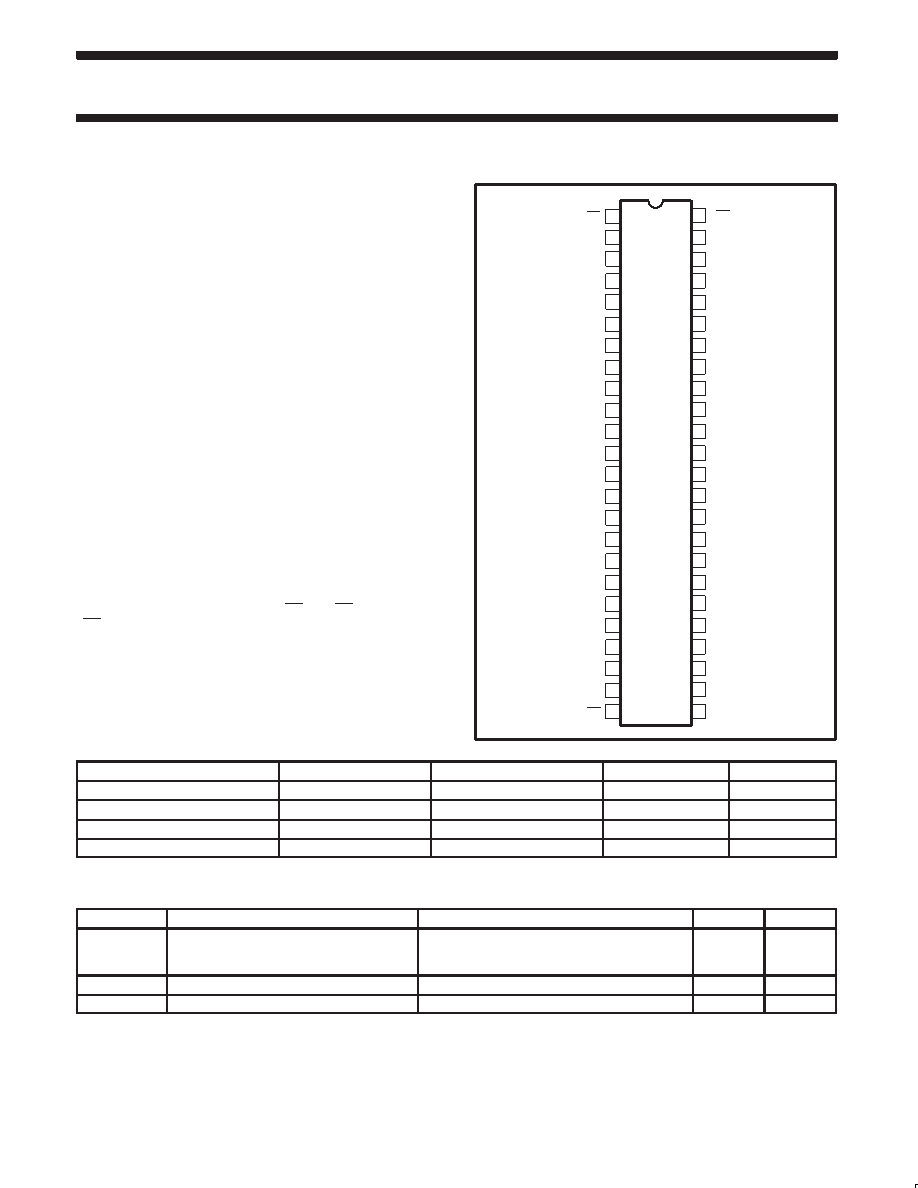

PIN CONFIGURATION

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

1OE

1Y0

1Y1

GND

1Y2

1Y3

VCC

2Y1

GND

2Y2

2Y3

3Y0

3Y1

GND

2Y0

3Y2

3Y3

VCC

4Y0

4Y1

4A1

4A0

VCC

3A3

3A2

GND

3A1

3A0

2A3

2A2

GND

2A1

2A0

VCC

1A3

1A2

GND

1A1

1A0

2OE

21

22

23

24

25

26

27

28

GND

4Y2

4Y3

4OE

3OE

4A3

4A2

GND

SW00194

ORDERING INFORMATION

PACKAGES

TEMPERATURE RANGE

OUTSIDE NORTH AMERICA

NORTH AMERICA

DWG NUMBER

48-Pin Plastic SSOP Type III

–40

°C to +85°C

74LVC162244A DL

VC162244A DL

SOT370-1

48-Pin Plastic TSSOP Type II

–40

°C to +85°C

74LVC162244A DGG

VC162244A DGG

SOT362-1

48-Pin Plastic SSOP Type III

–40

°C to +85°C

74LVCH162244A DL

VCH162244A DL

SOT370-1

48-Pin Plastic TSSOP Type II

–40

°C to +85°C

74LVCH162244A DGG

VCH162244A DGG

SOT362-1

QUICK REFERENCE DATA

GND = 0 V; Tamb = 25°C; tr = tf ≤ 2.5 ns

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

tPHL/tPLH

Propagation delay

1An to 1Yn;

2An to 2Yn

CL = 50pF

VCC = 3.3V

2.9

ns

CI

Input capacitance

5.0

pF

CPD

Power dissipation capacitance per buffer

VI = GND to VCC1

25

pF

NOTES:

1. CPD is used to determine the dynamic power dissipation (PD in mW):

PD = CPD × VCC2 × fi + S (CL × VCC2 × fo) where:

fi = input frequency in MHz; CL = output load capacity in pF;

fo = output frequency in MHz; VCC = supply voltage in V;

S (CL × VCC2 × fo) = sum of the outputs.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935237680112 | LVC/LCX/Z SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 935238700112 | LVC/LCX/Z SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 935238710118 | LVC/LCX/Z SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 935238750112 | LVC/LCX/Z SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

| 935237720118 | LVC/LCX/Z SERIES, 16 1-BIT DRIVER, TRUE OUTPUT, PDSO48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935241-0001 | 制造商: 功能描述: 制造商:DIGITRAN 功能描述: 制造商:undefined 功能描述: |

| 935241-1 | 制造商:DIGITRAN 功能描述: 制造商:DTRAN 功能描述: |

| 935245650125 | 制造商:NXP Semiconductors 功能描述:Inverter 1-Element CMOS 5-Pin TSSOP T/R |

| 935248-90 | 制造商:JANCO 功能描述:935248-90 |

| 9-3525-012 | 制造商:KEYSTONE 功能描述:MODIFIED 3525,VERSION E |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。