- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24785 > 935247300112 (NXP SEMICONDUCTORS) 8-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PDSO28 PDF資料下載

參數(shù)資料

| 型號(hào): | 935247300112 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, OTPROM, 16 MHz, MICROCONTROLLER, PDSO28 |

| 封裝: | 7.50 MM, PLASTIC, SO-28 |

| 文件頁數(shù): | 10/35頁 |

| 文件大小: | 243K |

| 代理商: | 935247300112 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

1997 Apr 16

18

Philips Semiconductors

Product specication

8-bit microcontrollers with DTMF generator,

8 kbytes OTP and 128 bytes EEPROM

PCD3755A; PCD3755E;

PCD3755F

8

DERIVATIVE INTERRUPTS

One derivative interrupt event is defined. It is controlled by

bits T2F and ET2I in the EPCR (see Tables 10 and 11).

The derivative interrupt event occurs when T2F is set. This

request is honoured under the following circumstances:

No interrupt routine proceeds

No external interrupt request is pending

The derivative interrupt is enabled

ET2I is set.

The derivative interrupt routine must include instructions

that will remove the cause of the derivative interrupt by

explicitly clearing T2F. If the derivative interrupt is not

used, T2F may directly be tested by the program.

Obviously, T2F can also be asserted under program

control, e.g. to generate a software interrupt.

9

TIMING

Although thePCD3755A, PCD3755E and PCD3755F

operate over a clock frequency range from 1 to 16 MHz,

fxtal = 3.58 MHz will usually be chosen to take full

advantage of the frequency generator section.

10 RESET

In addition to the conditions given in the

“PCD33xxA

Family” data sheet, all derivative registers are cleared in

the reset state.

11 IDLE MODE

In Idle mode, the frequency generator, the EEPROM and

the Timer 2 sections remain operative. Therefore, the

IDLE instruction may be executed while an erase and/or

write access to EEPROM is in progress.

12 STOP MODE

Since the oscillator is switched off, the frequency

generator, the EEPROM and the Timer 2 sections receive

no clock. It is suggested to clear both the HGF and the

LGF registers before entering Stop mode. This will cut off

the biasing of the internal amplifiers, considerably

reducing current requirements.

The Stop mode must not be entered while an erase

and/or write access to EEPROM is in progress. The STOP

instruction may only be executed when EWP in EPCR is

zero. The Timer 2 section is frozen during Stop mode.

After exit from Stop mode by a HIGH level on CE/T0,

Timer 2 proceeds from the held state.

13 INSTRUCTION SET RESTRICTIONS

As RAM space is restricted to 128 bytes, care should be

taken to avoid accesses to non-existing RAM locations.

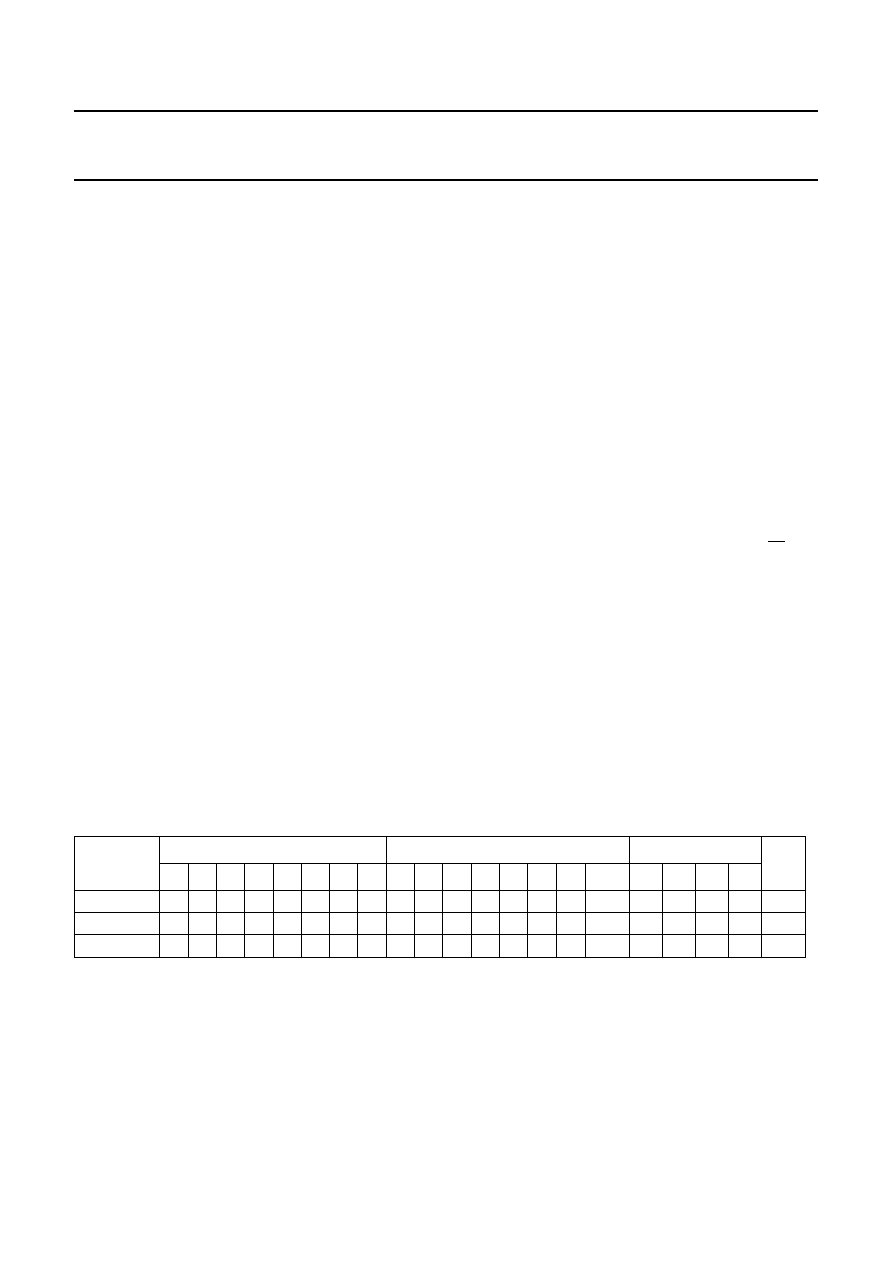

14 OVERVIEW OF PORT AND POWER-ON-RESET CONFIGURATION

Table 24 Port and Power-on-reset conguration

See note 1 and 2.

Notes

1. Port output drive: 1 = standard I/O; 2 = open-drain I/O, see

“PCD33xxA Family” data sheet.

2. Port state after reset: S = Set (HIGH) and R = Reset (LOW).

3. The Melody Output drive type is push-pull.

TYPE

PORT 0

PORT 1

PORT 2

VPOR

01234567012345

6

7

0123

PCD3755A

1S 1S 1S 1S 1S 1S 1S 1S 1S 1S 1S 1S 1S 1S 1R 1R(3)

2S

1.3 V

PCD3755E

1S 1S 1S 1S 1S 1S 1S 1S 2S 2S 2S 2S 2S 2S 1S 1S(3)

2S

1R

2.0 V

PCD3755F

1S 1S 1S 1S 1S 1S 1S 1S 1S 1S 1S 1S 1S 1S 1R 1R(3)

2S

2.0 V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 0676.400 | CONNECTOR ACCESSORY |

| 0676.500 | CONNECTOR ACCESSORY |

| 935196750112 | ABT SERIES, 18 1-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| 935203200118 | ABT SERIES, 18-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| 935196750118 | ABT SERIES, 18 1-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935248-90 | 制造商:JANCO 功能描述:935248-90 |

| 9-3525-012 | 制造商:KEYSTONE 功能描述:MODIFIED 3525,VERSION E |

| 935252-5 | 制造商:C-H 功能描述:935252-5 |

| 935257650112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY ICSUBS TO 935257650112 |

| 935260093112 | 制造商:NXP Semiconductors 功能描述:IC AVIC ADV BASESTATION 14SOIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。