- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36337 > 935261155112 (NXP SEMICONDUCTORS) HORIZ/VERT DEFLECTION IC, PDIP32 PDF資料下載

參數(shù)資料

| 型號: | 935261155112 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 偏轉 |

| 英文描述: | HORIZ/VERT DEFLECTION IC, PDIP32 |

| 封裝: | 0.400 INCH, PLASTIC, SOT-232, DIP-32 |

| 文件頁數(shù): | 19/63頁 |

| 文件大小: | 293K |

| 代理商: | 935261155112 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

1999 Jul 13

26

Philips Semiconductors

Product specication

I2C-bus autosync deection controllers for

PC/TV monitors

TDA4853; TDA4854

Notes

1. For duration of vertical blanking pulse see subheading ‘Vertical oscillator [oscillator frequency in application without

adjustment of free-running frequency ffr(V)]’.

2. Continuous blanking at CLBL (pin 16) will be activated, if one of the following conditions is true:

a) No horizontal flyback pulses at HFLB (pin 1) within a line

b) X-ray protection is triggered

c) Voltage at HPLL2 (pin 30) is low during soft start

d) Supply voltage at VCC (pin 10) is low

e) PLL1 unlocked while frequency-locked loop is in search mode.

3. Oscillator frequency is fmin when no sync input signal is present (continuous blanking at pins 16 and 17).

4. Loading of HPLL1 (pin 26) is not allowed.

5. Voltage at HPLL1 (pin 26) is fed to HBUF (pin 27) via a buffer. Disturbances caused by horizontal sync are removed

by an internal sample-and-hold circuit.

6. All vertical and EW adjustments in accordance with note 8, but VSIZE = 80% (register VSIZE = 63 and control

bit VOVSCN = 0).

7. Value of resistor at VREF (pin 23) may not be changed.

8. All vertical and EW adjustments are specified at nominal vertical settings; unless otherwise specified, which means:

a) VSIZE = 100% (register VSIZE = 127 and control bit VOVSCN = 0)

b) VSMOD = 0 (no EHT compensation)

Voff(VCC)

supply voltage level for

deactivation of BDRV, VOUT1,

VOUT2 and HUNLOCK; also

sets register SOFTST

VCC decreasing from

above typical 8.3 V

7.7

8.1

8.5

V

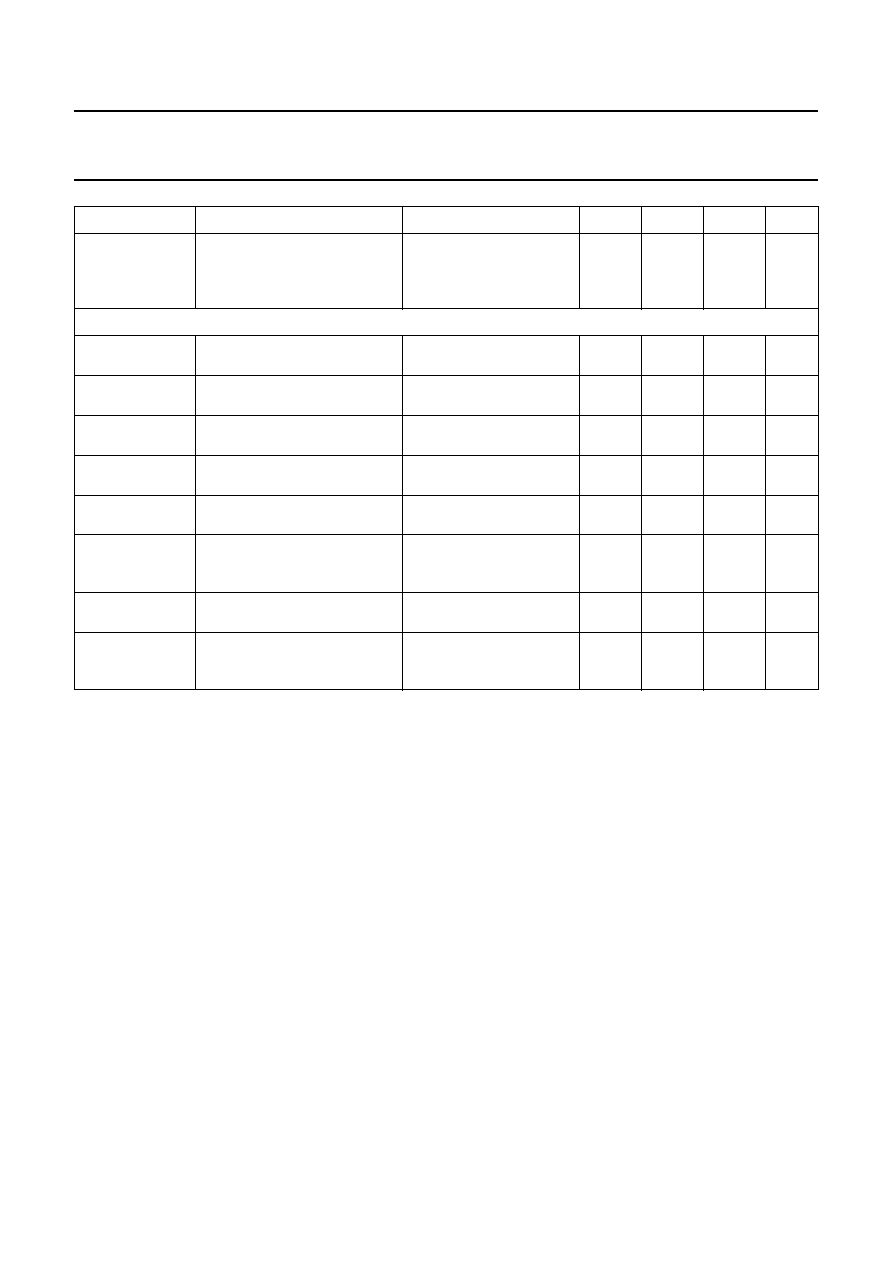

THRESHOLDS DERIVED FROM HPLL2 VOLTAGE

VHPLL2(blank)(ul)

upper limit voltage for

continuous blanking

4.7

V

VHPLL2(bduty)(ul)

upper limit voltage for variation

of BDRV duty cycle

3.4

V

VHPLL2(bduty)(ll)

lower limit voltage for variation

of BDRV duty cycle

2.8

V

VHPLL2(hduty)(ul)

upper limit voltage for variation

of HDRV duty cycle

2.8

V

VHPLL2(hduty)(ll)

lower limit voltage for variation

of HDRV duty cycle

1.7

V

VHPLL2(stby)(ll)

lower limit voltage for VOUT1

and VOUT2 to be active via

I2C-bus soft start

1.1

V

VHPLL2(stby)(ul)

upper limit voltage for standby

voltage

1

V

VHPLL2(stby)(ll)

lower limit voltage for VOUT1

and VOUT2 to be active via

external DC current

0

V

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

相關PDF資料 |

PDF描述 |

|---|---|

| 935261222557 | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 935261242118 | SERIAL INPUT LOADING, 20-BIT DAC, PDSO16 |

| 935261242112 | SERIAL INPUT LOADING, 20-BIT DAC, PDSO16 |

| 935261315112 | 2 CHANNEL(S), VOLUME CONTROL CIRCUIT, PDSO20 |

| 935261315118 | 2 CHANNEL(S), VOLUME CONTROL CIRCUIT, PDSO20 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 935262025112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935262217118 | 制造商:NXP Semiconductors 功能描述:Real Time Clock Serial 8-Pin SO T/R |

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。