- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24826 > 935263156518 (NXP SEMICONDUCTORS) 8-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | 935263156518 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | PLASTIC, QFP-80 |

| 文件頁數(shù): | 51/76頁 |

| 文件大小: | 567K |

| 代理商: | 935263156518 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當(dāng)前第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

Philips Semiconductors

Product specification

P83C557E4/P80C557E4/P89C557E4

Single-chip 8-bit microcontroller

1999 Mar 02

55

Example of user software (internal or external) that calls the

Page Erase routine in the boot ROM to erase a page in the

FEEPROM (32 bytes) starting at address location 1260H.

CLR EA

; Disable all interrupts

MOV DPTR, # 1260H

; Load page-address

MOV FMCON, # 4CH

; Load Page-Erase code

LCALL 0FFAAH

; Call Page-Erase routine

; in boot ROM (inherent delay

5 ms)

MOV FMCON, #00H

; Clear FMCON for security

SETB EA

; Enable interrupts again

Example of user software (internal or external) that calls the

Byte-Write routine in the boot ROM to write the content of R5 into

the FEEPROM address location 1263H.

CLR EA

; Disable all interrupts

MOV DPTR, # 1263H

; Load byte address

MOV A, R5

; Load byte to be written

MOV FMCON, # 45H

; Load byte-write code

LCALL 0FFADH

; Call byte-write routine

; in boot ROM (inherent

delay 2.5 ms)

MOV FMCON, #00H

; Clear FMCON for security

SETB EA

; Enable interrupts again

XRL A, R5

; Compare the “read-back” byte

JNZ ERROR

; Jump if verify error

8.4

Security

The security feature protects against software piracy and prevents

that the content of the FEEPROM can be read undesirable. The

Security Byte is located in the highest address location 7FFFH of

the FEEPROM.

The Security Byte should be 50H to activate and 00H or FFH to

deactivate the security feature. This security code is chosen in such

a way that single bit failures will not deactivate the security feature.

If the security feature is deactivated, then there are no access

restrictions to the FEEPROM.

If the security feature is activated, then the external program

memory has no access to the FEEPROM with the MOVC

instructions. Also bits FCB (3–0) of FMCON cannot be written by

external program code or boot ROM code. This prevents in-circuit

programming and verification. Only the Full Erase code can be

written to FCB (0–3) of FMCON. Note that for the internal program

code no restrictions exist if the security feature is activated. At the

end of a full erase operation the security feature is deactivated. Also

parallel programming and verify is inhibited if the security feature is

activated, only a full erase is possible. Note that the security mode

does not change immediately when the security code is written into

the security byte 7FFFH, but after a reset or power-on. This allows

the verification of the loaded code in the FEEPROM, including the

Security Byte.

8.5

Parallel Programming

Unlike standard EPROM programming, no high programming supply

voltage must be applied to the EA pin and only one programming

pulse must be applied to the ALE/WE pin. The parallel programming

mode is entered with the steady signals RST=1, PSEN=0, EA=1 and

SELXTAL1 = 1. The XTAL1,2 clock must have a frequency between

4 and 6MHz. The following table shows the logic levels for

programming, erasing, verifying and read signature.

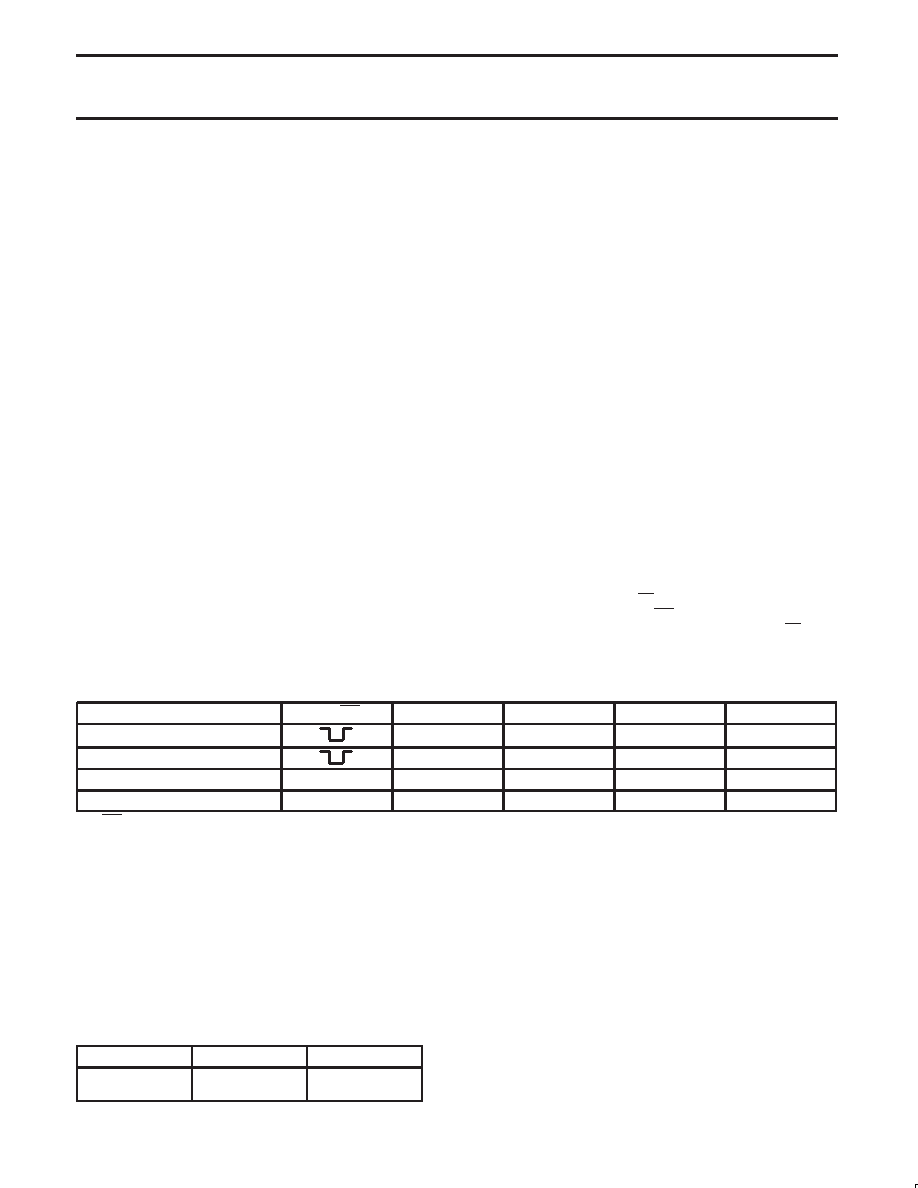

MODE

ALE/WE

P2.7

P2.6

P3.7

P3.6

Full erase

1

0

1

Program FEEPROM

1

0

1

Verify FEEPROM

1

0

1

Read signature

1

0

ALE/WE

Write Enable signal (program/erase), active low

P2.6, P2.7, P3.6, P3.7

control signals

Data and address bits:

P0.0 – P0.7

:

D0 – D7

Program data input / verify or read data output

P1.0 – P1.7

:

A0 – A7

Input low order address bits.

P2.0 – P2.5, P3.4

:

A8 – A14

Input high order address bits.

The P89C557E4 contains two signature bytes that can be read and

used by an EPROM programming system to identify the device.

These bytes are read by the same procedure as for a normal

verification of locations 30H and 31H, except that P3.6 and P3.7

need to be pulled to LOW.

ADDRESS

CONTENT

MEANING

30H

31H

15H

B5H

Philips

P89C557E4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 08-XC62H | TV 10C 10#20 PIN PLUG RECP |

| 935267931112 | AVC SERIES, 18 1-BIT DRIVER, TRUE OUTPUT, PDSO56 |

| 935267931118 | AVC SERIES, 18 1-BIT DRIVER, TRUE OUTPUT, PDSO56 |

| 935272534118 | AVC SERIES, 18 1-BIT DRIVER, TRUE OUTPUT, PDSO56 |

| 935272534112 | AVC SERIES, 18 1-BIT DRIVER, TRUE OUTPUT, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。