- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24813 > 935264448518 (NXP SEMICONDUCTORS) LVC/LCX/Z SERIES, 32 1-BIT DRIVER, TRUE OUTPUT, PBGA96 PDF資料下載

參數(shù)資料

| 型號: | 935264448518 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 總線收發(fā)器 |

| 英文描述: | LVC/LCX/Z SERIES, 32 1-BIT DRIVER, TRUE OUTPUT, PBGA96 |

| 封裝: | 13.5 X 5.5 MM, 1.05 MM HEIGHT, PLASTIC, SOT-536-1, FBGA-96 |

| 文件頁數(shù): | 9/16頁 |

| 文件大小: | 80K |

| 代理商: | 935264448518 |

1999 Nov 24

2

Philips Semiconductors

Product specication

32-bit transparent D-type latch with

5 V tolerant inputs/outputs; 3-state

74LVCH32373A

FEATURES

5 V tolerant inputs/outputs for interfacing with 5 V logic

Wide supply voltage range from 1.2 to 3.6 V

CMOS low power consumption

MULTIBYTE flow-trough standard pin-out architecture

Low inductance multiple power and ground pins for

minimum noise and ground bounce

Direct interface with TTL levels

Bus hold on data inputs

Typical output ground bounce voltage:

VOLP <0.8VatVCC = 3.3 V and Tamb =25 °C

Typical output undershoot voltage:

VOHV >2VatVCC = 3.3 V and Tamb =25 °C

Power off disables outputs, permitting live insertion

Packaged in plastic fine-pitch ball grid array package.

DESCRIPTION

The 74LVCH32373A is a high-performance, low-power,

low-voltage, Si-gate CMOS device, superior to most

advanced CMOS compatible TTL families.

The inputs can be driven from either 3.3 or 5 V devices.

In 3-state operation, outputs can handle 5 V. These

features allow the use of these devices in a mixed

3.3 or 5 V environment.

The 74LVCH32373A is a 32-bit transparent D-type latch

featuring separate D-type inputs for each latch and 3-state

outputs for bus oriented applications. One latch enable

(nLE) input and one output enable (nOE) are provided for

each octal. Inputs can be driven from either 3.3 or 5 V

devices.

The 74LVCH32373A consists of 4 sections of eight D-type

transparent latches with 3-state true outputs. When input

nLE is HIGH, data at the nDn inputs enter the latches. In

this condition the latches are transparent, i.e. a latch

output will change each time its corresponding D-input

changes.

When input nLE is LOW the latches store the information

that was present at the D-inputs one set-up time preceding

the HIGH-to-LOW transition of nLE. When input nOE is

LOW, the contents of the eight latches are available at the

outputs. When input nOE is HIGH, the outputs go to the

high-impedance OFF-state. Operation of the nOE input

does not affect the state of the latches.

The 74LVCH32373A bus hold data input circuits eliminate

the need for external pull-up resistors to hold unused

inputs.

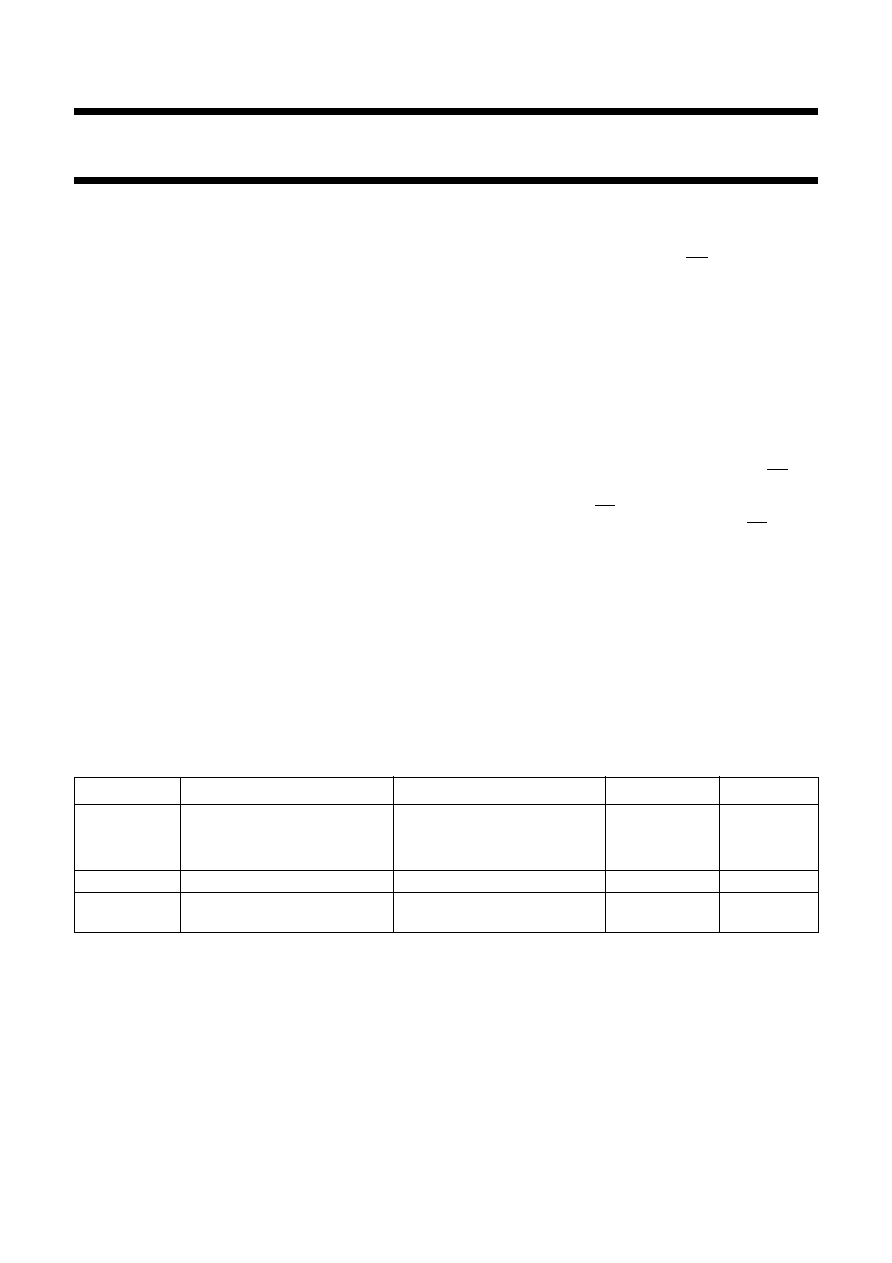

QUICK REFERENCE DATA

GND = 0 V; Tamb =25 °C; tr =tf ≤ 2.5 ns.

Note

1. CPD is used to determine the dynamic power dissipation (PD in W).

PD =CPD × VCC2 × fi + Σ (CL × VCC2 × fo) where:

fi = input frequency in MHz;

fo = output frequency in MHz;

CL = output load capacitance in pF;

VCC = supply voltage in Volts;

Σ (CL × VCC2 × fo) = sum of the outputs.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

tPHL/tPLH

propagation delay

nDn to nQn

CL = 50 pF; VCC = 3.3 V

3.0

ns

nLE to nQn

CL = 50 pF; VCC = 3.3 V

3.4

ns

CI

input capacitance

5.0

pF

CPD

power dissipation capacitance

per buffer

VI = GND to VCC; note 1

26

pF

相關PDF資料 |

PDF描述 |

|---|---|

| 935264448551 | LVC/LCX/Z SERIES, 32 1-BIT DRIVER, TRUE OUTPUT, PBGA96 |

| 08-350000-10 | SOCKET ADPTR SOIC/8PIN .300 DIP |

| 935264449557 | LVC/LCX/Z SERIES, QUAD 8-BIT DRIVER, TRUE OUTPUT, PBGA96 |

| 935264449518 | LVC/LCX/Z SERIES, 32 1-BIT DRIVER, TRUE OUTPUT, PBGA96 |

| 935264471518 | TELEPHONE SPEECH CKT, PQFP44 |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

發(fā)布緊急采購,3分鐘左右您將得到回復。