- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24820 > 935265560118 (NXP SEMICONDUCTORS) AHCT/VHCT SERIES, 8-BIT RIGHT SERIAL IN PARALLEL OUT SHIFT REGISTER, TRUE OUTPUT, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | 935265560118 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 計(jì)數(shù)移位寄存器 |

| 英文描述: | AHCT/VHCT SERIES, 8-BIT RIGHT SERIAL IN PARALLEL OUT SHIFT REGISTER, TRUE OUTPUT, PDSO16 |

| 封裝: | 4.40 MM, PLASTIC, MO-153, SOT-403-1, TSSOP-16 |

| 文件頁(yè)數(shù): | 12/20頁(yè) |

| 文件大?。?/td> | 103K |

| 代理商: | 935265560118 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

2000 Mar 15

2

Philips Semiconductors

Product specication

8-bit serial-in/serial or parallel-out shift

register with output latches; 3-state

74AHC595; 74AHCT595

FEATURES

ESD protection:

HBM EIA/JESD22-A114-A exceeds 2000 V

MM EIA/JESD22-A115-A exceeds 200 V

CDM EIA/JESD22-C101 exceeds 1000 V

Balanced propagation delays

All inputs have Schmitt-trigger actions

Inputs accept voltages higher than VCC

For AHC only: operates with CMOS input levels

For AHCT only: operates with TTL input levels

Specified from 40 to +85 °C and from40 to +125 °C.

APPLICATIONS

Serial-to-parallel data conversion

Remote control holding register.

DESCRIPTION

The 74AHC/AHCT595 are high-speed Si-gate CMOS

devices and are pin compatible with Low power Schottky

TTL (LSTTL). They are specified in compliance with

JEDEC standard No. 7A.

The 74AHC/AHCT595 is an 8-stage serial shift register

with a storage register and 3-state outputs. The shift

register has separate clocks.

Data is shifted on the positive-going transitions of the

SHCP input. The data in each register is transferred to the

storage register on a positive-going transition of the STCP

input. If both clocks are connected together, the shift

register will always be one clock pulse ahead of the

storage register.

The shift register has a serial input (DS) and a serial

standard output (Q7’) for cascading. It is also provided with

asynchronous reset (active LOW) for all 8 shift register

stages. The storage register has 8 parallel 3-state bus

driver outputs. Data in the storage register appears at the

output whenever the output enable input (OE) is LOW.

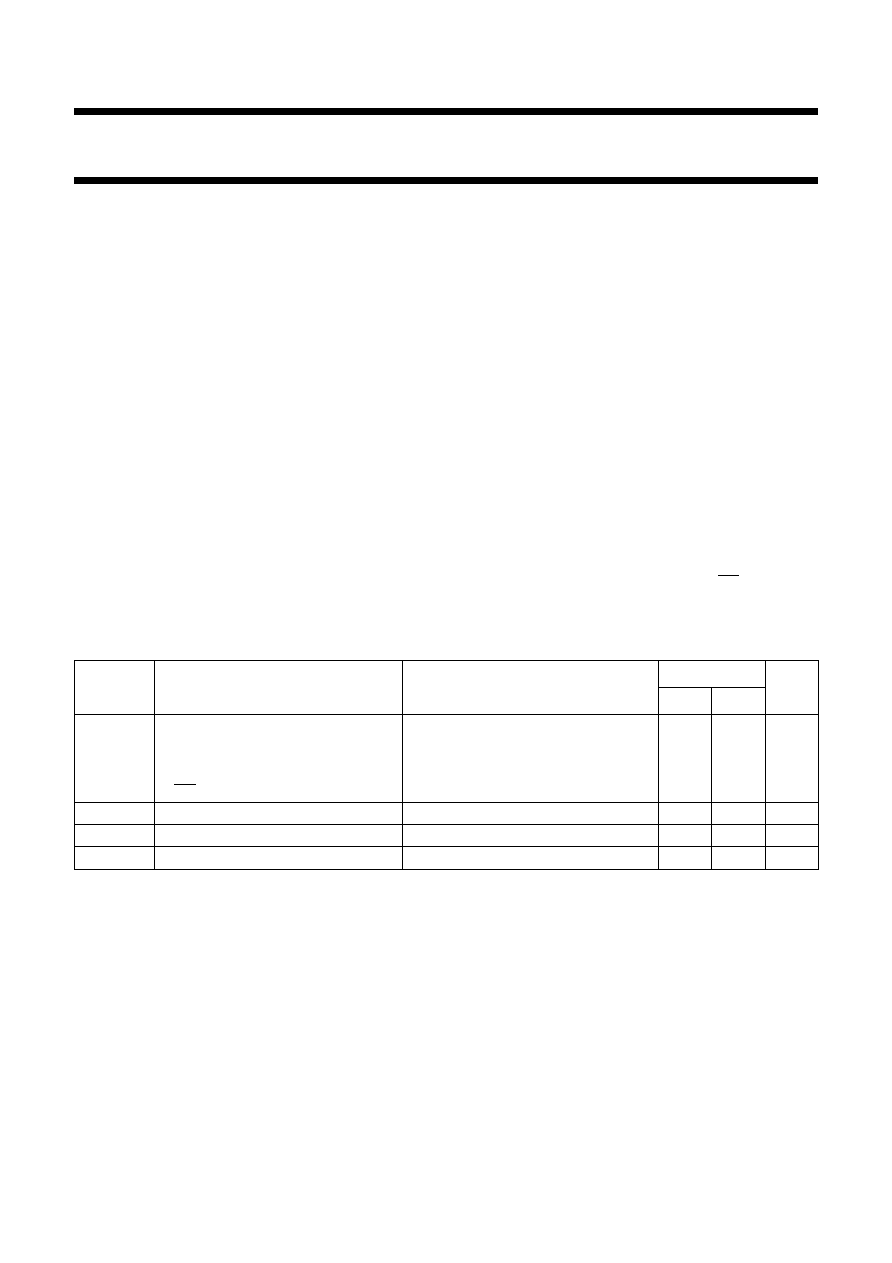

QUICK REFERENCE DATA

GND = 0 V; Tamb =25 °C; tr =tf ≤ 3.0 ns.

Notes

1. CPD is used to determine the dynamic power dissipation (PD in W).

PD =CPD × VCC2 × fi + ∑ (CL × VCC2 × fo) where:

fi = input frequency in MHz;

fo = output frequency in MHz;

∑ (CL × VCC2 × fo) = sum of outputs;

CL = output load capacitance in pF;

VCC = supply voltage in Volts.

2. The condition is VI = GND to VCC.

3. All 9 outputs switching.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

AHC

AHCT

tPHL/tPLH

propagation delay

CL = 15 pF; VCC =5V

SHCP to Q7’

4.0

3.8

ns

STCP to Qn

4.2

4.0

ns

MR to Q7’

4.4

4.6

ns

CI

input capacitance

3.0

pF

fmax

maximum clock frequency

170

MHz

CPD

power dissipation capacitance

CL = 50 pF; f = 1 MHz; notes 1, 2 and 3 180

190

pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 08-52-0132 | KK 156 TERM CRP 18-22 AWG ANTIFISH TIN |

| 08-58-0136 | Crimp Socket Contact; Wire Size (AWG):22-18; Contact Material:Phosphor Bronze |

| 08-50-0008 | 8500008 |

| 08-50-0023 | KK 156 TERM CRP 18-22 AWG ANTIFISH TIN |

| 08-50-0705 | KK 156 TERM CRP 18-22 AWG ANTIFISH TIN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。