- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24836 > 935266681115 (NXP SEMICONDUCTORS) LVC/LCX/Z SERIES, 1-INPUT NON-INVERT GATE, PDSO5 PDF資料下載

參數(shù)資料

| 型號: | 935266681115 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 門電路 |

| 英文描述: | LVC/LCX/Z SERIES, 1-INPUT NON-INVERT GATE, PDSO5 |

| 封裝: | PLASTIC, SC-88A, 5 PIN |

| 文件頁數(shù): | 12/19頁 |

| 文件大?。?/td> | 137K |

| 代理商: | 935266681115 |

2003 Mar 07

2

Philips Semiconductors

Product specication

Buffer with open-drain output

74LVC1G07

FEATURES

Wide supply voltage range from 1.65 to 5.5 V

High noise immunity

Complies with JEDEC standard:

– JESD8-7 (1.65 to 1.95 V)

– JESD8-5 (2.3 to 2.7 V)

– JESD8B/JESD36 (2.7 to 3.6 V).

24 mA output drive (VCC = 3.0 V)

CMOS low power consumption

Latch-up performance exceeds 250 mA

Direct interface with TTL levels

Inputs accept voltages up to 5 V

Multiple package options

ESD protection:

HBM EIA/JESD22-A114-A exceeds 2000 V

MM EIA/JESD22-A115-A exceeds 200 V

Specified from 40 to +85 °C and 40 to +125 °C.

DESCRIPTION

The 74LVC1G07 is a high-performance, low-power,

low-voltage, Si-gate CMOS device, superior to most

advanced CMOS compatible TTL families.

The input can be driven from either 3.3 or 5 V devices.

This feature allows the use of this device as translator in a

mixed 3.3 and 5 V environment.

Schmitt trigger action at the input makes the circuit tolerant

for slower input rise and fall time.

The 74LVC1G07 provides the non-inverting buffer.

The output of the device is an open drain and can be

connected to other open-drain outputs to implement

active-LOW wired-OR or active-HIGH wired-AND

functions.

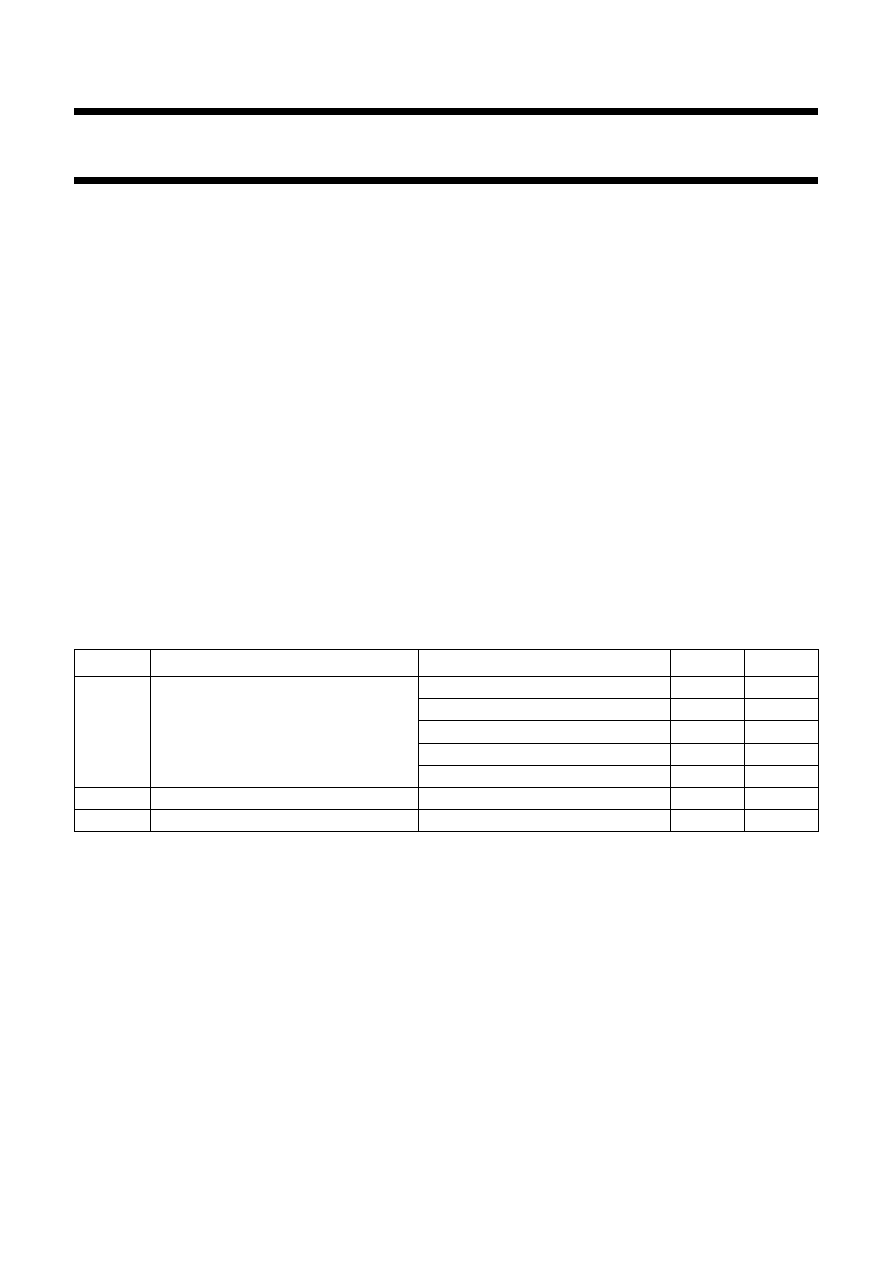

QUICK REFERENCE DATA

GND = 0 V; Tamb =25 °C; tr =tf ≤ 2.5 ns.

Notes

1. CPD is used to determine the dynamic power dissipation (PD in W).

PD =CPD × VCC2 × fi × N+ Σ(CL × VCC2 × fo) where:

fi = input frequency in MHz;

fo = output frequency in MHz;

CL = output load capacitance in pF;

VCC = supply voltage in Volts;

N = total switching outputs;

Σ(CL × VCC2 × fo) = sum of the outputs.

2. The condition is VI = GND to VCC.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

tPLZ/tPZL

propagation delay inputs A to output Y

VCC = 1.8 V; CL = 30 pF; RL =1k

2.6

ns

VCC = 2.5 V; CL = 30 pF; RL = 500

1.7

ns

VCC = 2.7 V; CL = 50 pF; RL = 500

2.3

ns

VCC = 3.3 V; CL = 50 pF; RL = 500

2.2

ns

VCC = 5.0 V; CL = 50 pF; RL = 500

1.6

ns

CI

input capacitance

5

pF

CPD

power dissipation capacitance per gate

VCC = 3.3 V; notes 1 and 2

7

pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935272239112 | AVC SERIES, 20 1-BIT DRIVER, TRUE OUTPUT, PDSO56 |

| 935272239118 | AVC SERIES, 20 1-BIT DRIVER, TRUE OUTPUT, PDSO56 |

| 935272775118 | 8 I/O, PIA-GENERAL PURPOSE, PQCC16 |

| 935270674118 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

| 935270674112 | 8 I/O, PIA-GENERAL PURPOSE, PDSO16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。