- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36338 > 935266896557 (NXP SEMICONDUCTORS) 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | 935266896557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | ADC |

| 英文描述: | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| 封裝: | PLASTIC, SOT-317-2, QFP-64 |

| 文件頁數(shù): | 10/40頁 |

| 文件大小: | 250K |

| 代理商: | 935266896557 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

1999 Feb 24

18

Philips Semiconductors

Product specication

Triple high-speed Analog-to-Digital

Converter (ADC)

TDA8752A

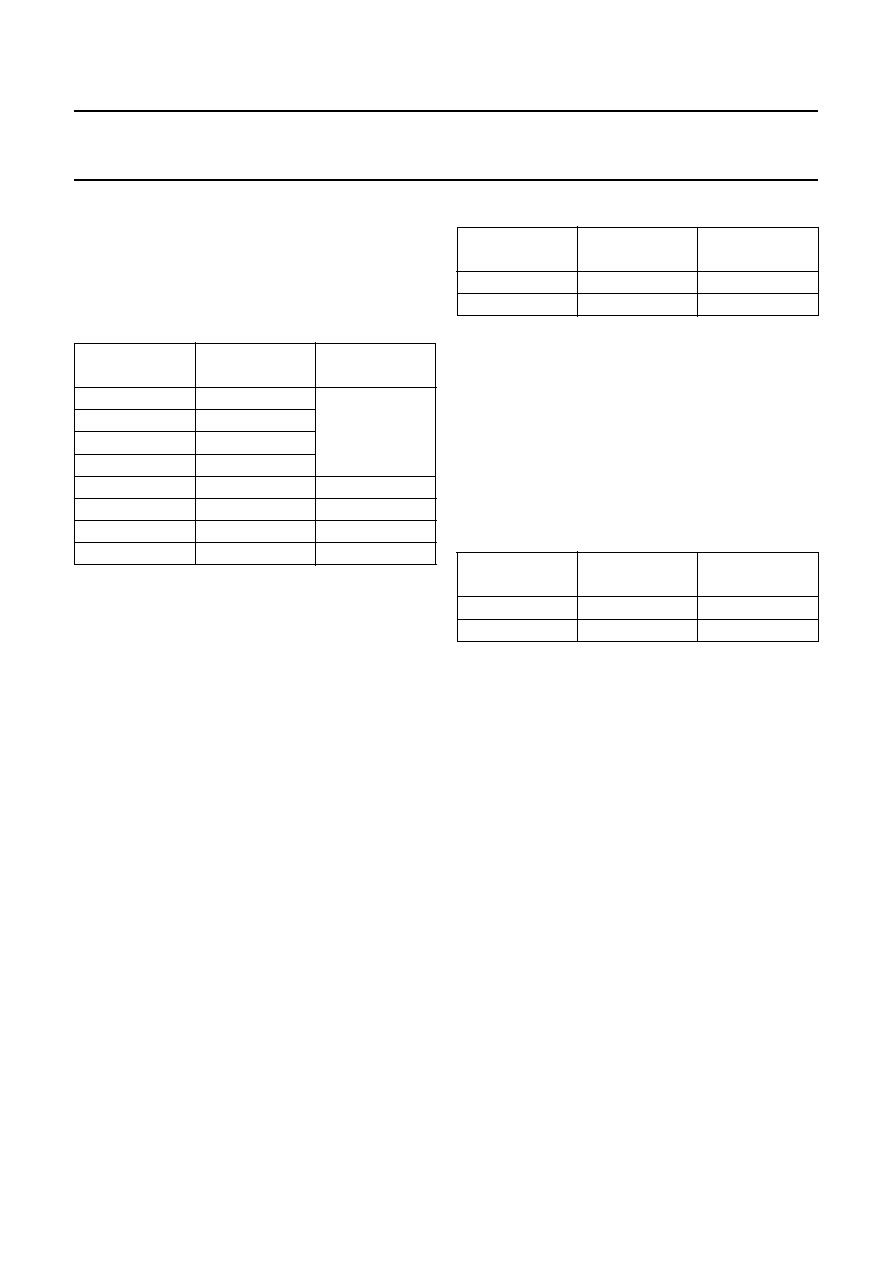

OFFSET REGISTER

This register controls the clamp level for the

RGB channels. The relationship between the

programming code and the level of the clamp code is given

in Table 2.

Table 2

Coding

The default programmed value is:

Programmed code = 127

Clamp code = 0

ADC output = 0.

COARSE AND FINE REGISTERS

These two registers enable the gain control, the AGC gain

with the coarse register and the reference voltage with the

fine register. The coarse register programming equation is

as follows:

Where: Vref = 2.5 V.

The gain correspondence is given in Table 3. The gain is

linear with reference to the programming code (NFINE = 0).

PROGRAMMED

CODE

CLAMP CODE

ADC OUTPUT

0

63.5

underow

1

63

2

62.5

↓↓

127

0

↓↓↓

254

63.5

63 or 64

255

64

GAIN

N

COARSE

1

+

V

ref 1

N

FINE

32

16

×

-------------------

–

----------------------------------------------

1

16

------

×

N

COARSE

1

+

V

ref 512

N

FINE

–

()

-------------------------------------------------

32

×

=

Table 3

Gain correspondence (COARSE)

The default programmed value is as follows:

N

COARSE =32

Gain = 0.825

Vi to be full-scale = 1.212.

To modulate this gain, the fine register is programmed

using the above equation. With a full-scale ADC input, the

fine register resolution is a 1

2LSB peak-to-peak

(see Table 4 for NCOARSE = 32).

Table 4

Gain correspondence (FINE)

The default programmed value is: NFINE =0.

CONTROL REGISTER

COAST and HSYNC signals can be inverted by setting the

I2C-bus control bits V level and H level respectively. When

V level and H level are set to zero respectively, COAST

and HSYNC are active HIGH.

The bit ‘edge’ defines the rising or falling edge of CKREF

to synchronise the PLL. It will be on the rising edge if the

bit is at logic 0 and on the falling edge if the bit is at logic 1.

The bits Up and Do are used for the test, to force the

charge pump current. These bits have to be logic 0 during

normal use.

The bits Ip0, Ip1 and Ip2 control the charge pump current,

to increase the bandwidth of the PLL, as shown in Table 5.

NCOARSE

GAIN

Vi TO BE

FULL-SCALE

32

0.825

1.212

99

2.5

0.4

NFINE

GAIN

Vi TO BE

FULL-SCALE

0

0.825

1.212

31

0.878

1.139

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935262255551 | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| 935262254557 | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| 935262318518 | COLOR SIGNAL ENCODER, PQFP44 |

| 935262318557 | COLOR SIGNAL ENCODER, PQFP44 |

| 935262321518 | COLOR SIGNAL ENCODER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

發(fā)布緊急采購,3分鐘左右您將得到回復。