- 您現(xiàn)在的位置:買賣IC網 > PDF目錄24862 > 950211BFLF (INTEGRATED DEVICE TECHNOLOGY INC) 205 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號: | 950211BFLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產生/分配 |

| 英文描述: | 205 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 0.300 INCH, GREEN, MO-118, SSOP-56 |

| 文件頁數(shù): | 18/23頁 |

| 文件大小: | 214K |

| 代理商: | 950211BFLF |

4

Integrated

Circuit

Systems, Inc.

ICS950211

0465E—05/17/05

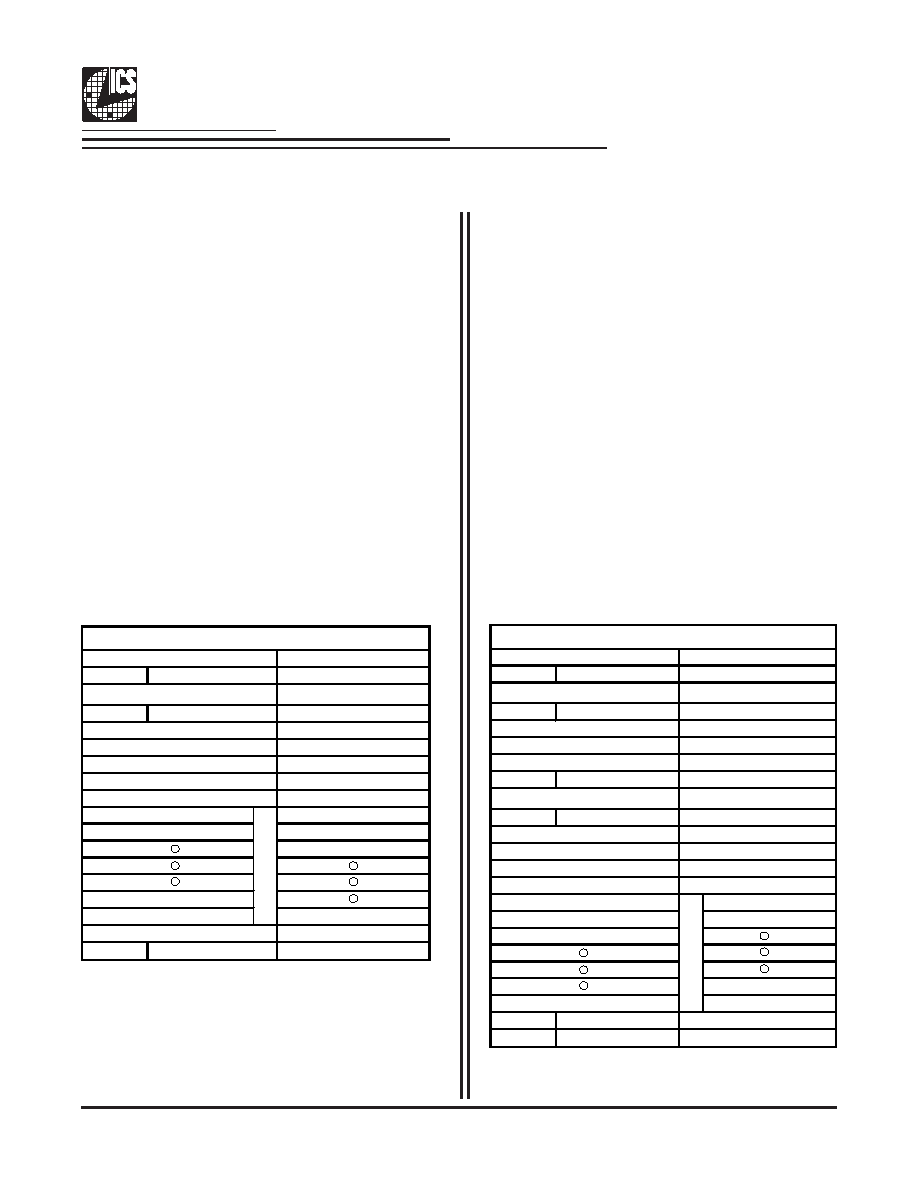

General I

2C serial interface information

How to Write:

Controller (host) sends a start bit.

Controller (host) sends the write address D2

(H)

ICS clock will

acknowledge

Controller (host) sends the begining byte location = N

ICS clock will

acknowledge

Controller (host) sends the data byte count = X

ICS clock will

acknowledge

Controller (host) starts sending

Byte N through

Byte N + X -1

(see Note 2)

ICS clock will

acknowledge each byte one at a time

Controller (host) sends a Stop bit

How to Read:

Controller (host) will send start bit.

Controller (host) sends the write address D2

(H)

ICS clock will

acknowledge

Controller (host) sends the begining byte

location = N

ICS clock will

acknowledge

Controller (host) will send a separate start bit.

Controller (host) sends the read address D3

(H)

ICS clock will

acknowledge

ICS clock will send the data byte count = X

ICS clock sends

Byte N + X -1

ICS clock sends

Byte 0 through byte X (if X

(H)

was written to byte 8).

Controller (host) will need to acknowledge each byte

Controllor (host) will send a not acknowledge bit

Controller (host) will send a stop bit

*See notes on the following page.

ICS (Slave/Receiver)

T

WR

ACK

P

stoP bit

X

By

te

Index Block Write Operation

Slave Address D2(H)

Beginning Byte = N

WRite

starT bit

Controller (Host)

Byte N + X - 1

Data Byte Count = X

Beginning Byte N

T

starT bit

WR

WRite

RT

Repeat starT

RD

ReaD

Beginning Byte N

Byte N + X - 1

N

Not acknowledge

PstoP bit

Slave Address D3(H)

Index Block Read Operation

Slave Address D2(H)

Beginning Byte = N

ACK

Data Byte Count = X

ACK

ICS (Slave/Receiver)

Controller (Host)

X

By

te

ACK

相關PDF資料 |

PDF描述 |

|---|---|

| 08053C103KA72A | General Specifications |

| 950211BFLFT | 205 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 950211BFT | 205 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 08053C103KA74A | General Specifications |

| 950218AFLFT | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 950211BFLFT | 功能描述:時鐘發(fā)生器及支持產品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 950211BGLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 950211BGLF Phased Locked Loop (PLL) |

| 950-212 | 制造商:Mitutoyo Corporation 功能描述:SPRING DIVIDER; Instrument Type:Spring Divider; Measuring Range Max:6" ;RoHS Compliant: NA |

| 9502-12INX180YDS | 制造商:3M Electronic Products Division 功能描述:70006170149 |

| 950-213 | 制造商:Mitutoyo Corporation 功能描述:SPRING DIVIDER, 8" |

發(fā)布緊急采購,3分鐘左右您將得到回復。