- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25563 > 9DB108YFT (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 PDF資料下載

參數(shù)資料

| 型號(hào): | 9DB108YFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 封裝: | ROHS COMPLIANT, MO-118, SSOP-48 |

| 文件頁數(shù): | 10/16頁 |

| 文件大小: | 144K |

| 代理商: | 9DB108YFT |

3

Integrated

Circuit

Systems, Inc.

ICS9DB108

(Not recommended for new designs)

0723G—12/02/08

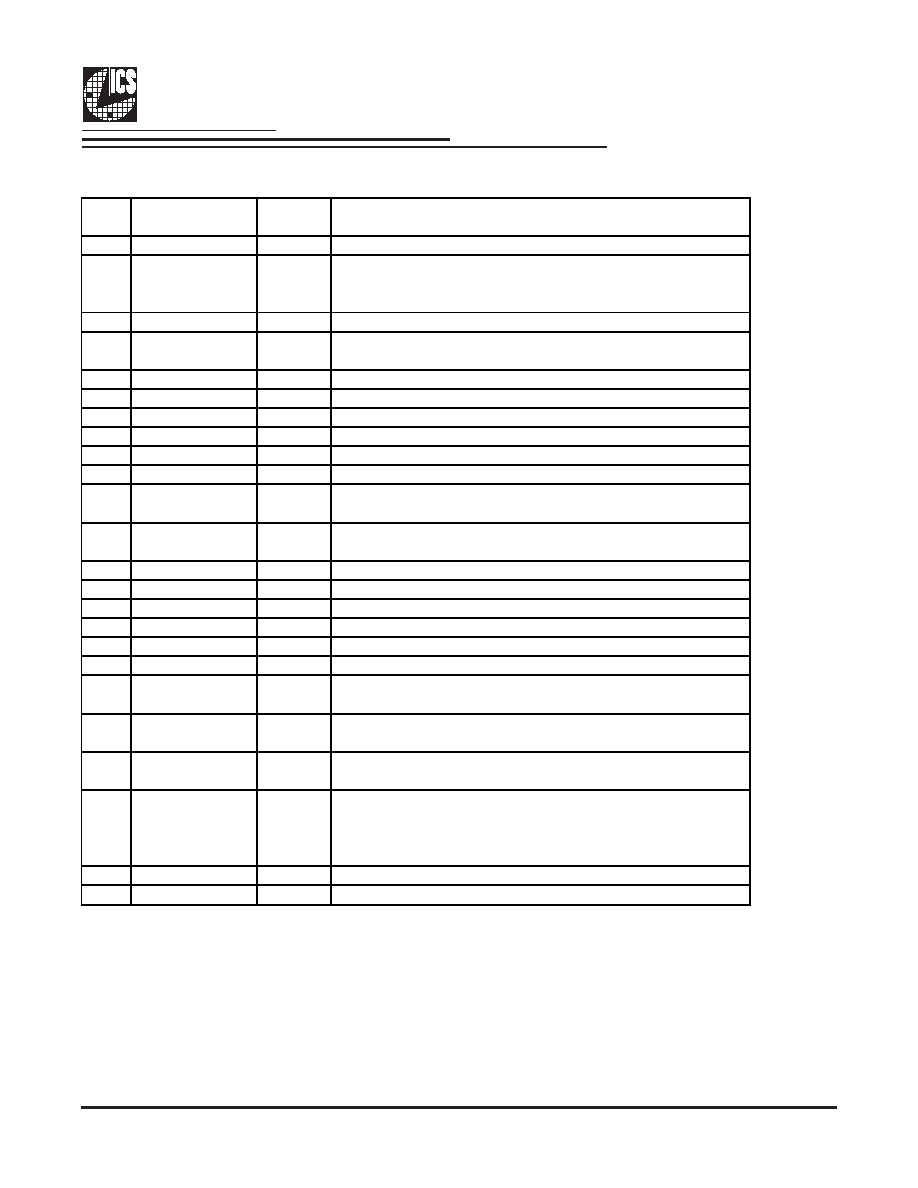

Pin Description (Continued)

PIN #

PIN NAME

PIN TYPE

DESCRIPTION

25

GND

PWR

Ground pin.

26

PD#

IN

Asynchronous active low input pin used to power down the

device. The internal clocks are disabled and the VCO and the

crystal are stopped.

27

SRC_STOP#

IN

Active low input to stop diff outputs.

28

HIGH_BW#

PWR

3.3V input for selecting PLL Band Width

0 = High, 1= Low

29

DIF_4#

OUT

0.7V differential complement clock outputs

30

DIF_4

OUT

0.7V differential true clock outputs

31

VDD

PWR

Power supply, nominal 3.3V

32

GND

PWR

Ground pin.

33

DIF_5#

OUT

0.7V differential complement clock outputs

34

DIF_5

OUT

0.7V differential true clock outputs

35

OE_5

IN

Active high input for enabling outputs.

0 = tri-state outputs, 1= enable outputs

36

OE_6

IN

Active high input for enabling outputs.

0 = tri-state outputs, 1= enable outputs

37

DIF_6#

OUT

0.7V differential complement clock outputs

38

DIF_6

OUT

0.7V differential true clock outputs

39

VDD

PWR

Power supply, nominal 3.3V

40

GND

PWR

Ground pin.

41

DIF_7#

OUT

0.7V differential complement clock outputs

42

DIF_7

OUT

0.7V differential true clock outputs

43

OE_4

IN

Active high input for enabling outputs.

0 = tri-state outputs, 1= enable outputs

44

OE_7

IN

Active high input for enabling outputs.

0 = tri-state outputs, 1= enable outputs

45

LOCK

OUT

3.3V output indicating PLL Lock Status. This pin goes high

when lock is achieved.

46

IREF

IN

This pin establishes the reference current for the differential

current-mode output pairs. This pin requires a fixed precision

resistor tied to ground in order to establish the appropriate

current. 475 ohms is the standard value.

47

GNDA

PWR

Ground pin for the PLL core.

48

VDDA

PWR

3.3V power for the PLL core.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9DB108YGLNT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB108YFLNT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB1200CGLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO64 |

| 9DB1233AGLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 12 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO64 |

| 9DB1904BKLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 19 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9DB1200BGLF | 制造商:Integrated Device Technology Inc 功能描述:PCIE GEN2 BUFFERS - Rail/Tube |

| 9DB1200C | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Twelve Output Differential Buffer for PCIe Gen1/Gen2, QPI, and FBDIMM |

| 9DB1200CGLF | 功能描述:時(shí)鐘緩沖器 12 OUTPUT PCIE GEN2 BUFFER w/QPI RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB1200CGLFT | 功能描述:時(shí)鐘緩沖器 12 OUTPUT PCIE GEN2 BUFFER w/QPI RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB1233 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Twelve Output Differential Buffer for PCIe Gen3 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。