- 您現(xiàn)在的位置:買賣IC網 > PDF目錄4453 > A1010B-2PQ100C (Microsemi SoC)IC FPGA 1200 GATES 100-PQFP COM PDF資料下載

參數(shù)資料

| 型號: | A1010B-2PQ100C |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 12/98頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 1200 GATES 100-PQFP COM |

| 標準包裝: | 66 |

| 系列: | ACT™ 1 |

| LAB/CLB數(shù): | 295 |

| 輸入/輸出數(shù): | 57 |

| 門數(shù): | 1200 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 100-BQFP |

| 供應商設備封裝: | 100-PQFP(14x20) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

2

H i g h -R e lia b i lity, L o w -R is k S o lu t i o n

Actel builds the most reliable field programmable gate arrays

(FPGAs) in the industry, with overall antifuse reliability

ratings

of

less

than

10

Failures-In-Time

(FITs),

corresponding to a useful life of more than 40 years. Actel

FPGAs have been production proven, with more than five

million devices shipped and more than one trillion antifuses

manufactured. Actel devices are fully tested prior to

shipment, with an outgoing defect level of less than 100 ppm.

(Further reliability data is available in the Actel Device

Reliability Report, at http://www.actel.com/hirel).

Be ne f i t s

Mi ni m i zed C o s t Ri s k

With Actel’s line of development tools, designers can produce

as many chips as they choose for just the cost of the device

itself. There will be no NRE charges to cut into the

development budget each time a new design is tried.

Mi ni m i zed T i m e R i s k

After the design is entered, placement and routing is

automatic, and programming the device takes only about 5 to

15 minutes for an average design. Designers save time in the

design entry process by using tools with which they are

familiar.

Mi ni m i zed R e l i abi l i ty R i s k

The PLICE antifuse is a one-time programmable, nonvolatile

connection.

Since

Actel

devices

are

permanently

programmed, no downloading from EPROM or SRAM storage

is required. Inadvertent erasure is impossible, and there is no

need to reload the program after power disruptions.

Fabrication using a low-power CMOS process means cooler

junction temperatures. Actel’s non-PLD architecture delivers

lower dynamic operating current. Our reliability tests show a

very low failure rate of 6.6 FITs at 90°C junction temperature

with no degradation in AC performance. Special stress testing

at wafer test eliminates infant mortalities prior to packaging.

M i ni m i zed S ecu ri ty R i s k

Reverse engineering of programmed Actel devices from

optical or electrical data is extremely difficult. Programmed

antifuses cannot be identified from a photograph or by using

an SEM. The antifuse map cannot be deciphered either

electrically or by microprobing. Each device has a silicon

signature that identifies its origins, down to the wafer lot and

fabrication facility.

M i ni m i zed T e s ti ng Ri s k

Unprogrammed Actel parts are extensively tested at the

factory. Routing tracks, logic modules, and programming,

debug and test circuits are 100 percent tested before

shipment. AC performance is ensured by special speed path

tests, and programming circuitry is verified on test antifuses.

During the programming process, an algorithm is run to

ensure that all antifuses are correctly programmed. In

addition, Actel’s Silicon Explorer diagnostic tool uses

ActionProbe circuitry, allowing 100 percent observability of

all internal nodes to check and debug the design.

Act e l F P GA D e s c r i pt i o n

The Actel families of FPGAs offer a variety of packages,

speed/performance characteristics, and processing levels for

use in all high reliability and military applications. Devices

are implemented in a silicon gate, two-level metal CMOS

process, utilizing Actel’s PLICE antifuse technology. This

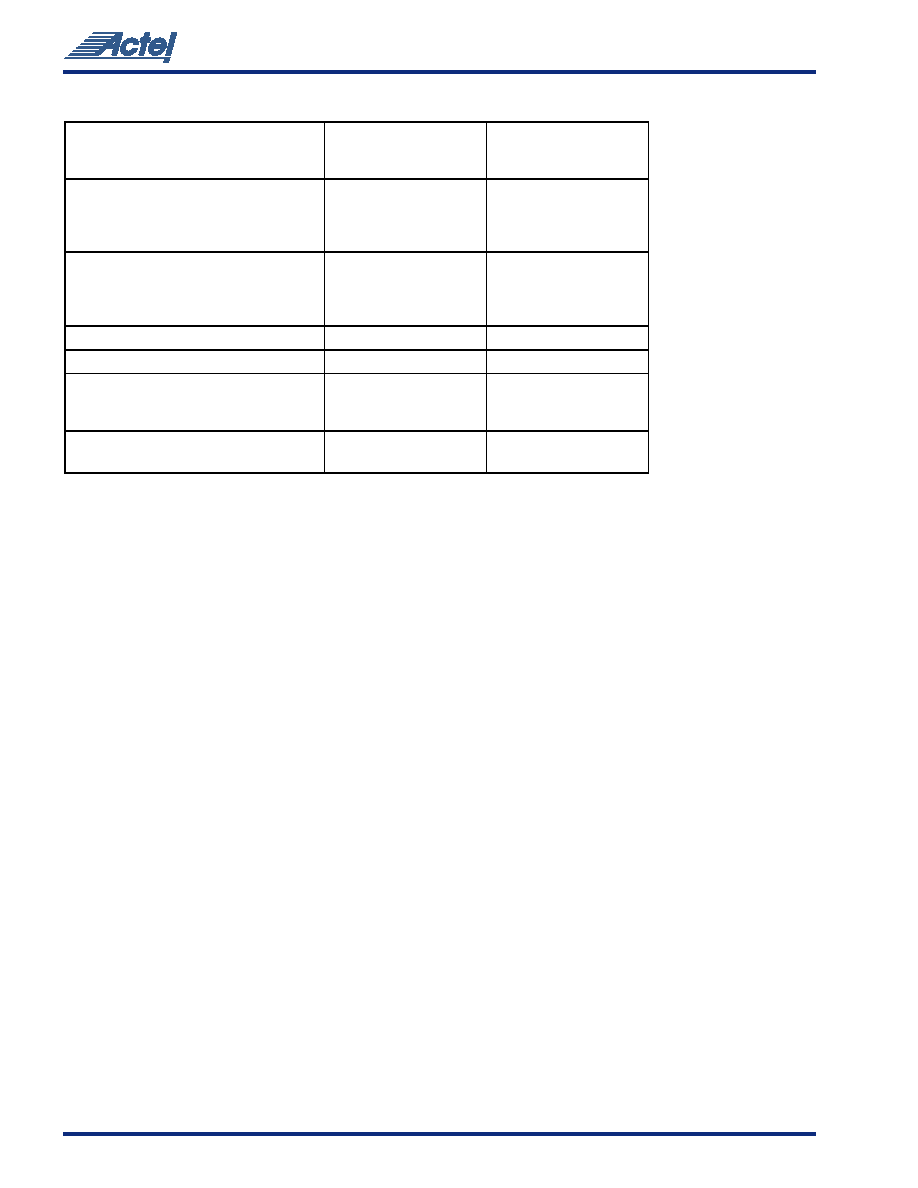

P r o d u c t F a m ily P r o f ile

Family

ACT 2

ACT 1

Device

A1240A

A1280A

A1010B

A1020B

Capacity

System Gates

Logic Gates

SRAM Bits

6,000

4,000

NA

12,000

8,000

NA

1,800

1,200

NA

3,000

2,000

NA

Logic Modules

S-Modules

C-Modules

Decode

684

348

336

NA

1,232

624

608

NA

295

—

295

NA

547

—

547

NA

Flip-Flops (maximum)

568

998

147

273

User I/Os (maximum)

104

140

57

69

Packages (by pin count)

CPGA

CQFP

132

—

176

172

84

—

84

Performance

System Speed (maximum)

40 MHz

20 MHz

相關PDF資料 |

PDF描述 |

|---|---|

| 5745174-3 | CONN BACKSHELL DB37 DIE CAST |

| A42MX09-2PQ160 | IC FPGA MX SGL CHIP 14K 160-PQFP |

| A42MX09-2PQG160 | IC FPGA MX SGL CHIP 14K 160-PQFP |

| RSC60DRTN | CONN EDGECARD 120PS DIP .100 SLD |

| 5745173-2 | CONN BACKSHELL DB25 DIE CAST |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| A1010B-2PQ100I | 功能描述:IC FPGA 1200 GATES 100-PQFP IND RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ACT™ 1 標準包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計:- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應商設備封裝:484-FPBGA(27X27) |

| A1010B-2PQ84B | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ACT 1 Series FPGAs |

| A1010B-2PQ84C | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ACT 1 Series FPGAs |

| A1010B-2PQ84I | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ACT 1 Series FPGAs |

| A1010B-2PQ84M | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ACT 1 Series FPGAs |

發(fā)布緊急采購,3分鐘左右您將得到回復。