- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄294787 > A32400DX-2BG313C FPGA, 2526 CLBS, 40000 GATES, PBGA313 PDF資料下載

參數(shù)資料

| 型號(hào): | A32400DX-2BG313C |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 2526 CLBS, 40000 GATES, PBGA313 |

| 封裝: | BGA-313 |

| 文件頁數(shù): | 12/22頁 |

| 文件大小: | 217K |

| 代理商: | A32400DX-2BG313C |

2

timing analysis, user programming, and debug and diagnostic

probe capabilities. In addition, Designer 3.0 provides the

DirectTime tool which provides deterministic as well as

controllable timing. DirectTime allows the designer to

specify the performance requirements of individual paths and

system clock(s). Using these specifications, the software will

automatically optimize the placement and routing of the logic

to meet these constraints. Included with Designer 3.0 is

Actel’s ACTgen Macro Builder. ACTgen allows the

designer to quickly build fast, efficient logic functions such

as counters, adders, FIFOs, and RAM.

The Designer Series tools provide designers the capability to

move up to High-Level Description Languages, such as

VHDL and Verilog, or use schematic design entry with

interfaces to most EDA tools. Designer Series 3.0 is

supported on the following development platforms: 386/486

and Pentium PC, Sun and HP workstations. The software

provides CAE interfaces to Cadence, Escalade, Exemplar

Logic, IST, Mentor Graphics OrCAD, Synopsys, and

Viewlogic design environments. Additional development

tools are supported through Actel’s Industry Alliance

Program, including DATA I/O (ABEL FPGA) and MINC.

Actel’s FPGAs are an ideal solution for shortening the system

design and development cycle and offers a cost-effective

alternative for low volume production runs. The 3200DX

devices are an excellent choice for integrating logic that is

currently implemented in TTL, PALs, CPLDs and FPGAs.

Some example applications include high-speed controllers

and address decoding, peripheral bus interfaces, DSP, and

co-processor functions.

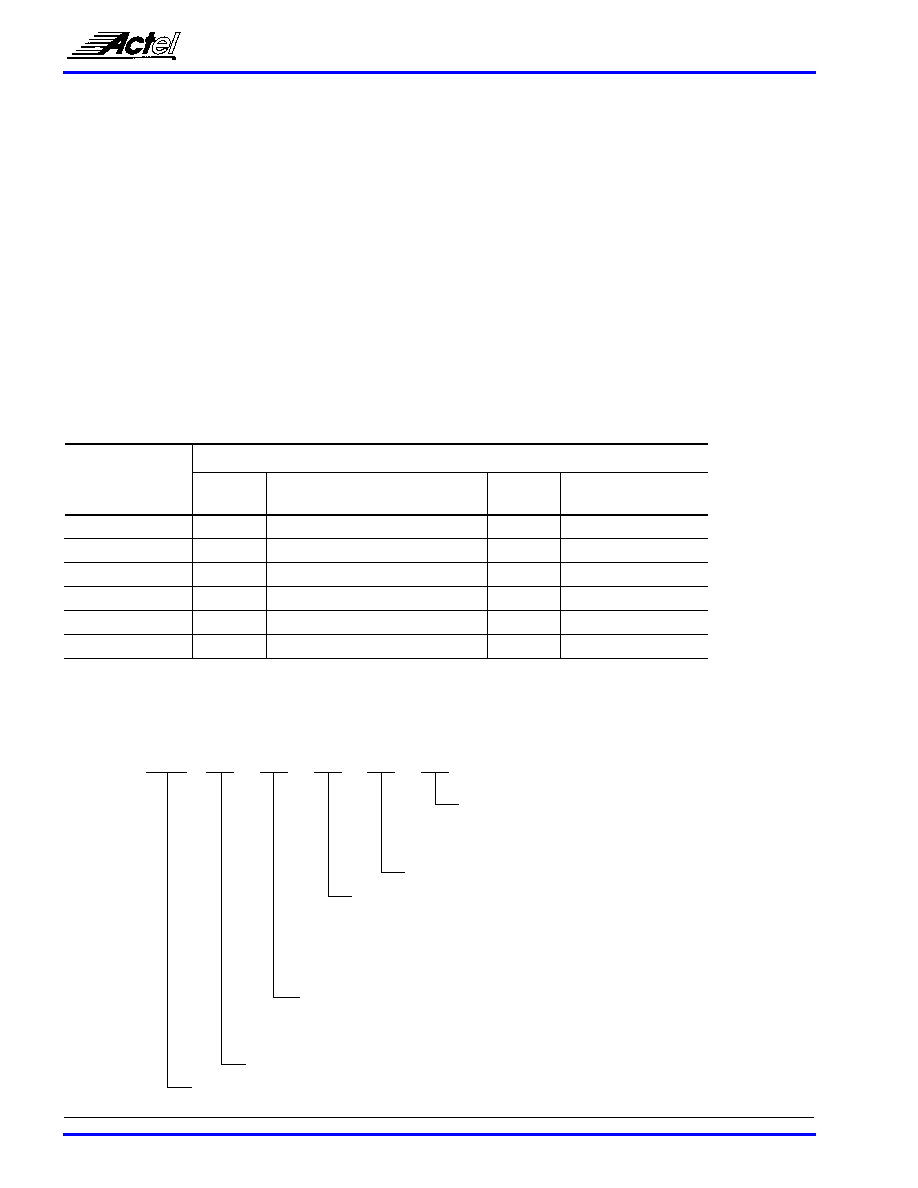

Device Resources

Package Definitions (Consult your local Actel Sales Representative for product availability.)

PLCC = Plastic Leaded Chip Carrier, PQFP = Plastic Quad Flat Pack, TQFP = Thin Quad Flat Pack, BGA = Ball Grid Array

Ordering Information

User I/Os

Device Series

PLCC

84-pin

PQFP

160-pin

PQFP

208-pin

PQFP

240-pin

TQFP

176-pin

BGA

225-pin

BGA

313-pin

A3265DX

72

125

—

126

—

A32100DX

72

125

156

—

151

156

—

A32140DX

—

125

176

—

151

176

—

A32200DX

—

176

TBD

—

TBD

206

A32300DX

—

TBD

—

254

A32400DX

—

TBD

—

TBD

Application (Temperature Range)

C = Commercial (0 to +70

°C)

I

= Industrial (–40 to +85

°C)

PP = Pre-Production

Package Type

PL = Plastic J-Leaded Chip Carrier

PQ = Plastic Quad Flatpack

TQ = Thin (1.4 mm) Quad Flatpack

RQ = Power Quad Flatpack

BG = Ball Grid Array

Speed Grade

Blank = Standard Speed

–1 = Approximately 15% faster than Standard

–2 = Approximately 25% faster than Standard

Part Number

Package Lead Count

A32200

–

PQ

208

C

1

DX

Sub Family

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A32400DX-2BG313I | FPGA, 2526 CLBS, 40000 GATES, PBGA313 |

| A32400DX-2PQ240C | FPGA, 2526 CLBS, 40000 GATES, PQFP240 |

| A32400DX-2PQ240I | FPGA, 2526 CLBS, 40000 GATES, PQFP240 |

| A32400DX-BG313C | FPGA, 2526 CLBS, 40000 GATES, PBGA313 |

| A32400DX-BG313I | FPGA, 2526 CLBS, 40000 GATES, PBGA313 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A32400DX-2RQ240C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A32400DX-2RQ240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A32400DX-3RQ240C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A32400DX-3RQ240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A32400DX-FRQ240C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。