- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨疯常IC缍�(w菐ng) > PDF鐩寗4497 > A3P600L-1FG256 (Microsemi SoC)IC FPGA 1KB FLASH 600K 256-FBGA PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉锛� | A3P600L-1FG256 |

| 寤犲晢锛� | Microsemi SoC |

| 鏂囦欢闋佹暩(sh霉)锛� | 26/242闋� |

| 鏂囦欢澶�?銆�?/td> | 0K |

| 鎻忚堪锛� | IC FPGA 1KB FLASH 600K 256-FBGA |

| 妯�(bi膩o)婧�(zh菙n)鍖呰锛� | 90 |

| 绯诲垪锛� | ProASIC3L |

| RAM 浣嶇附瑷堬細 | 110592 |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 177 |

| 闁€鏁�(sh霉)锛� | 600000 |

| 闆绘簮闆诲锛� | 1.14V ~ 1.575 V |

| 瀹夎椤炲瀷锛� | 琛ㄩ潰璨艰 |

| 宸ヤ綔婧害锛� | 0°C ~ 70°C |

| 灏佽/澶栨锛� | 256-LBGA |

| 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 256-FPBGA锛�17x17锛� |

绗�1闋�绗�2闋�绗�3闋�绗�4闋�绗�5闋�绗�6闋�绗�7闋�绗�8闋�绗�9闋�绗�10闋�绗�11闋�绗�12闋�绗�13闋�绗�14闋�绗�15闋�绗�16闋�绗�17闋�绗�18闋�绗�19闋�绗�20闋�绗�21闋�绗�22闋�绗�23闋�绗�24闋�绗�25闋�鐣�(d膩ng)鍓嶇26闋�绗�27闋�绗�28闋�绗�29闋�绗�30闋�绗�31闋�绗�32闋�绗�33闋�绗�34闋�绗�35闋�绗�36闋�绗�37闋�绗�38闋�绗�39闋�绗�40闋�绗�41闋�绗�42闋�绗�43闋�绗�44闋�绗�45闋�绗�46闋�绗�47闋�绗�48闋�绗�49闋�绗�50闋�绗�51闋�绗�52闋�绗�53闋�绗�54闋�绗�55闋�绗�56闋�绗�57闋�绗�58闋�绗�59闋�绗�60闋�绗�61闋�绗�62闋�绗�63闋�绗�64闋�绗�65闋�绗�66闋�绗�67闋�绗�68闋�绗�69闋�绗�70闋�绗�71闋�绗�72闋�绗�73闋�绗�74闋�绗�75闋�绗�76闋�绗�77闋�绗�78闋�绗�79闋�绗�80闋�绗�81闋�绗�82闋�绗�83闋�绗�84闋�绗�85闋�绗�86闋�绗�87闋�绗�88闋�绗�89闋�绗�90闋�绗�91闋�绗�92闋�绗�93闋�绗�94闋�绗�95闋�绗�96闋�绗�97闋�绗�98闋�绗�99闋�绗�100闋�绗�101闋�绗�102闋�绗�103闋�绗�104闋�绗�105闋�绗�106闋�绗�107闋�绗�108闋�绗�109闋�绗�110闋�绗�111闋�绗�112闋�绗�113闋�绗�114闋�绗�115闋�绗�116闋�绗�117闋�绗�118闋�绗�119闋�绗�120闋�绗�121闋�绗�122闋�绗�123闋�绗�124闋�绗�125闋�绗�126闋�绗�127闋�绗�128闋�绗�129闋�绗�130闋�绗�131闋�绗�132闋�绗�133闋�绗�134闋�绗�135闋�绗�136闋�绗�137闋�绗�138闋�绗�139闋�绗�140闋�绗�141闋�绗�142闋�绗�143闋�绗�144闋�绗�145闋�绗�146闋�绗�147闋�绗�148闋�绗�149闋�绗�150闋�绗�151闋�绗�152闋�绗�153闋�绗�154闋�绗�155闋�绗�156闋�绗�157闋�绗�158闋�绗�159闋�绗�160闋�绗�161闋�绗�162闋�绗�163闋�绗�164闋�绗�165闋�绗�166闋�绗�167闋�绗�168闋�绗�169闋�绗�170闋�绗�171闋�绗�172闋�绗�173闋�绗�174闋�绗�175闋�绗�176闋�绗�177闋�绗�178闋�绗�179闋�绗�180闋�绗�181闋�绗�182闋�绗�183闋�绗�184闋�绗�185闋�绗�186闋�绗�187闋�绗�188闋�绗�189闋�绗�190闋�绗�191闋�绗�192闋�绗�193闋�绗�194闋�绗�195闋�绗�196闋�绗�197闋�绗�198闋�绗�199闋�绗�200闋�绗�201闋�绗�202闋�绗�203闋�绗�204闋�绗�205闋�绗�206闋�绗�207闋�绗�208闋�绗�209闋�绗�210闋�绗�211闋�绗�212闋�绗�213闋�绗�214闋�绗�215闋�绗�216闋�绗�217闋�绗�218闋�绗�219闋�绗�220闋�绗�221闋�绗�222闋�绗�223闋�绗�224闋�绗�225闋�绗�226闋�绗�227闋�绗�228闋�绗�229闋�绗�230闋�绗�231闋�绗�232闋�绗�233闋�绗�234闋�绗�235闋�绗�236闋�绗�237闋�绗�238闋�绗�239闋�绗�240闋�绗�241闋�绗�242闋�

ProASIC3L Low Power Flash FPGAs

Revision 13

2-105

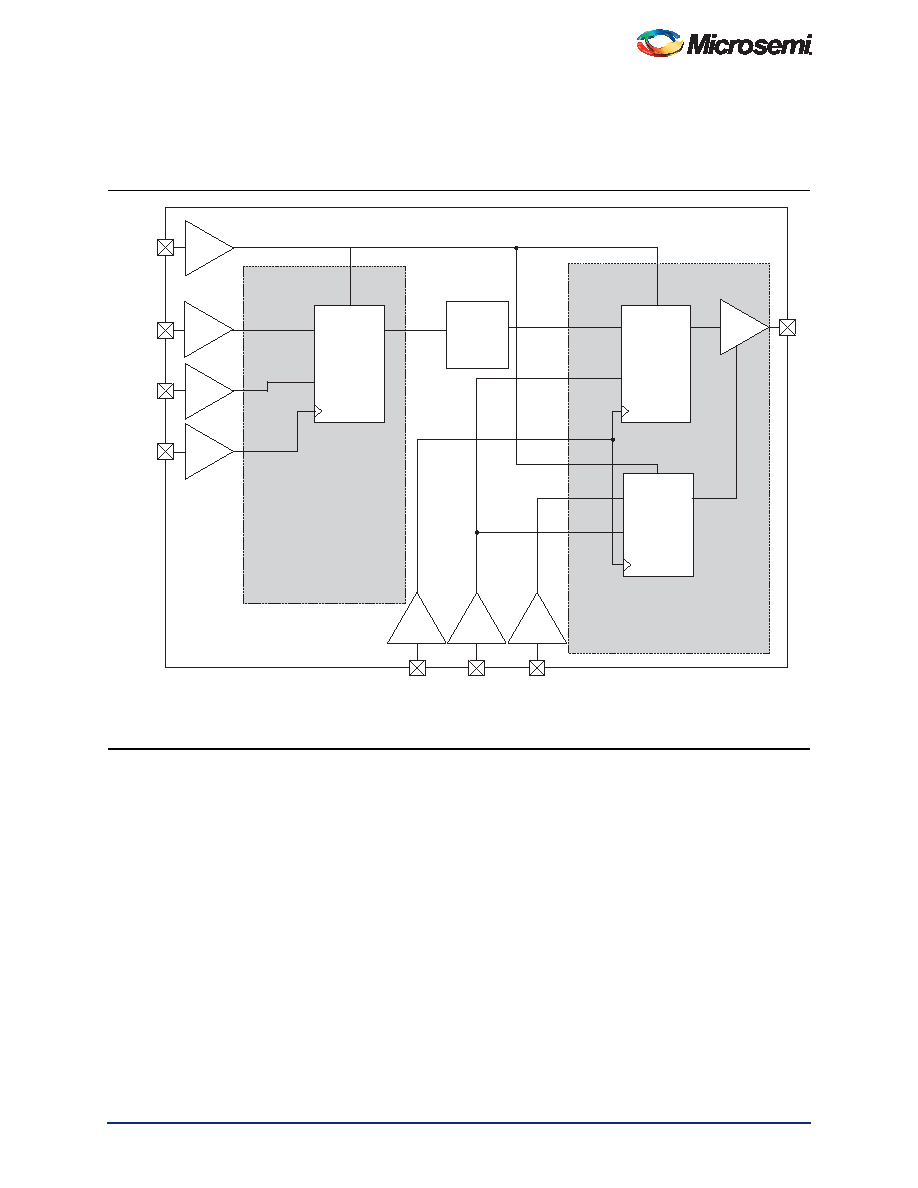

I/O Register Specifications

Fully Registered I/O Buffers with Synchronous Enable and

Asynchronous Preset

Figure 2-26 Timing Model of Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

INBUF

TRIBUF

CLKBUF

INBUF

CLKBUF

Data Input I/O Register with:

Active High Enable

Active High Preset

Positive-Edge Triggered

Data Output Register and

Enable Output Register with:

Active High Enable

Active High Preset

Postive-Edge Triggered

Pad

Out

CLK

Enable

Preset

Data_out

Data

EOUT

DOUT

Enable

CLK

DQ

DFN1E1P1

PRE

DQ

DFN1E1P1

PRE

DQ

DFN1E1P1

PRE

D_Enable

A

B

C

D

E

F

G

H

I

J

L

K

Y

Core

Array

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| ACC43DRTN-S734 | CONN EDGECARD 86POS DIP .100 SLD |

| ACC43DRTH-S734 | CONN EDGECARD 86POS DIP .100 SLD |

| GSC65DRTF | CONN EDGECARD 130PS DIP .100 SLD |

| GMC65DRTF | CONN EDGECARD 130PS DIP .100 SLD |

| AMM24DRSI-S288 | CONN EDGECARD 48POS .156 EXTEND |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| A3P600L-1FG256I | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 600K 256-FBGA RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪锛� 绯诲垪:ProASIC3L 妯�(bi膩o)婧�(zh菙n)鍖呰:40 绯诲垪:SX-A LAB/CLB鏁�(sh霉):6036 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�:- 杓稿叆/杓稿嚭鏁�(sh霉):360 闁€鏁�(sh霉):108000 闆绘簮闆诲:2.25 V ~ 5.25 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 70°C 灏佽/澶栨:484-BGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:484-FPBGA锛�27X27锛� |

| A3P600L-1FG484 | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 600K 484-FBGA RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪锛� 绯诲垪:ProASIC3L 妯�(bi膩o)婧�(zh菙n)鍖呰:90 绯诲垪:ProASIC3 LAB/CLB鏁�(sh霉):- 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�:36864 杓稿叆/杓稿嚭鏁�(sh霉):157 闁€鏁�(sh霉):250000 闆绘簮闆诲:1.425 V ~ 1.575 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:-40°C ~ 125°C 灏佽/澶栨:256-LBGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:256-FPBGA锛�17x17锛� |

| A3P600L-1FG484I | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 600K 484-FBGA RoHS:鍚� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪锛� 绯诲垪:ProASIC3L 妯�(bi膩o)婧�(zh菙n)鍖呰:40 绯诲垪:SX-A LAB/CLB鏁�(sh霉):6036 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�:- 杓稿叆/杓稿嚭鏁�(sh霉):360 闁€鏁�(sh霉):108000 闆绘簮闆诲:2.25 V ~ 5.25 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 70°C 灏佽/澶栨:484-BGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:484-FPBGA锛�27X27锛� |

| A3P600L-1FGG144 | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 600K 144-FBGA RoHS:鏄� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪锛� 绯诲垪:ProASIC3L 妯�(bi膩o)婧�(zh菙n)鍖呰:90 绯诲垪:ProASIC3 LAB/CLB鏁�(sh霉):- 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�:36864 杓稿叆/杓稿嚭鏁�(sh霉):157 闁€鏁�(sh霉):250000 闆绘簮闆诲:1.425 V ~ 1.575 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:-40°C ~ 125°C 灏佽/澶栨:256-LBGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:256-FPBGA锛�17x17锛� |

| A3P600L-1FGG144I | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 600K 144-FBGA RoHS:鏄� 椤炲垾:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫村彲绶ㄧ▼闁€闄e垪锛� 绯诲垪:ProASIC3L 妯�(bi膩o)婧�(zh菙n)鍖呰:90 绯诲垪:ProASIC3 LAB/CLB鏁�(sh霉):- 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�:36864 杓稿叆/杓稿嚭鏁�(sh霉):157 闁€鏁�(sh霉):250000 闆绘簮闆诲:1.425 V ~ 1.575 V 瀹夎椤炲瀷:琛ㄩ潰璨艰 宸ヤ綔婧害:-40°C ~ 125°C 灏佽/澶栨:256-LBGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:256-FPBGA锛�17x17锛� |

鐧�(f膩)甯冪穵鎬ラ噰璩硷紝3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�