- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄164976 > A40MX04-FVQ80 FPGA, 547 CLBS, 6000 GATES, 48 MHz, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | A40MX04-FVQ80 |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 547 CLBS, 6000 GATES, 48 MHz, PQFP80 |

| 封裝: | 1 MM HEIGHT, PLASTIC, VQFP-80 |

| 文件頁(yè)數(shù): | 32/124頁(yè) |

| 文件大小: | 3142K |

| 代理商: | A40MX04-FVQ80 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)當(dāng)前第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)

40MX and 42MX FPGA Families

v6.1

1-9

Fixed Capacitance Values for MX FPGAs (pF)

Test Circuitry and Silicon Explorer II Probe

MX devices contain probing circuitry that provides built-

in access to every node in a design, via the use of Silicon

Explorer II. Silicon Explorer II is an integrated hardware

and software solution that, in conjunction with the

Designer software, allow users to examine any of the

internal nets of the device while it is operating in a

prototyping or a production system. The user can probe

into an MX device without changing the placement and

routing of the design and without using any additional

resources. Silicon Explorer II's noninvasive method does

not alter timing or loading effects, thus shortening the

debug cycle and providing a true representation of the

device under actual functional situations.

Silicon

Explorer

II

samples

data

at

100

MHz

(asynchronous) or 66 MHz (synchronous). Silicon Explorer

II attaches to a PC's standard COM port, turning the PC

into a fully functional 18-channel logic analyzer. Silicon

Explorer II allows designers to complete the design

verification

process

at

their

desks

and

reduces

verification time from several hours per cycle to a few

seconds.

Silicon Explorer II is used to control the MODE, DCLK, SDI

and SDO pins in MX devices to select the desired nets for

debugging. The user simply assigns the selected internal

nets in the Silicon Explorer II software to the PRA/PRB

output pins for observation. Probing functionality is

activated when the MODE pin is held HIGH.

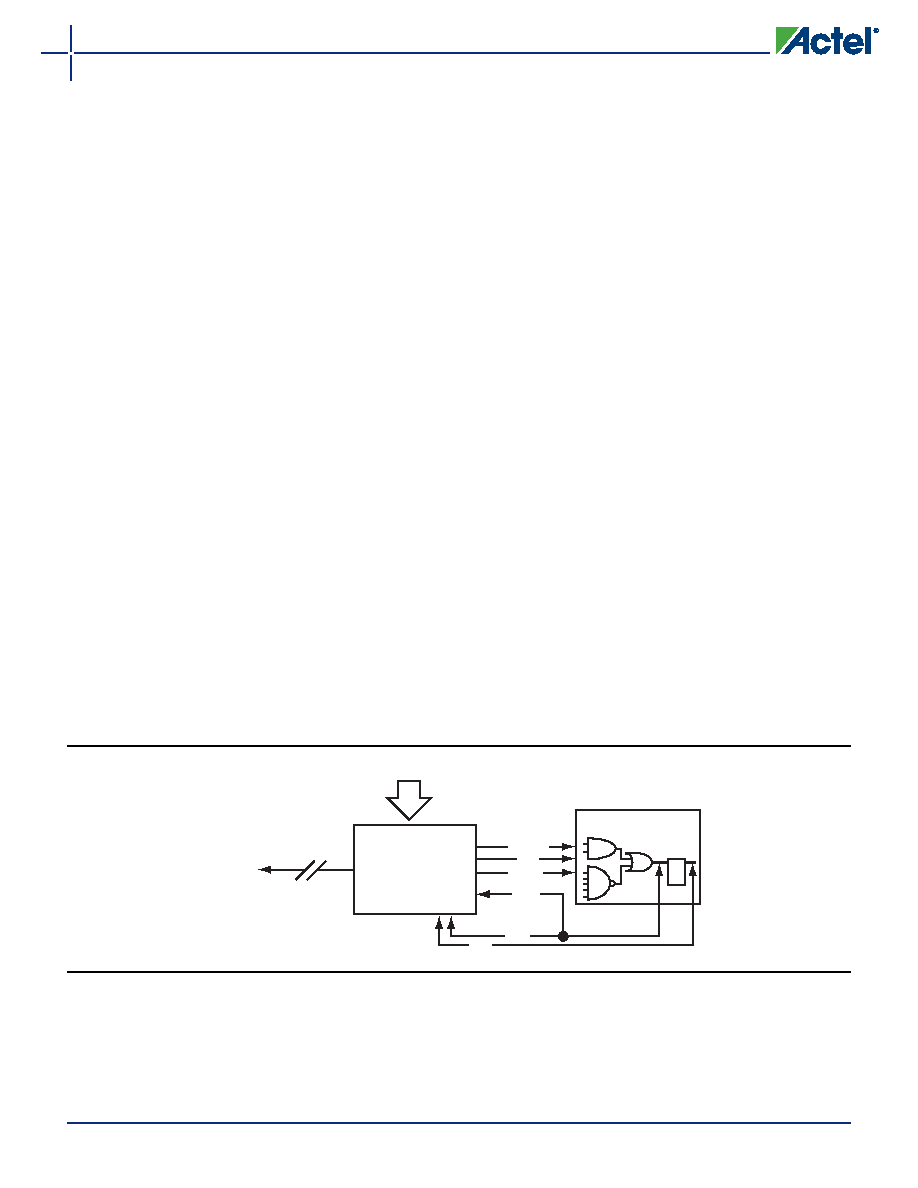

Figure 1-12 illustrates the interconnection between

Silicon Explorer II and 40MX devices, while Figure 1-13

on page 1-10 illustrates the interconnection between

Silicon Explorer II and 42MX devices

To allow for probing capabilities, the security fuses must

not be programmed. (Refer to <zBlue>“User Security”

section on page 6 for the security fuses of 40MX and

42MX devices). Table 2 on page 1-10 summarizes the

possible device configurations for probing.

PRA and PRB pins are dual-purpose pins. When the

"Reserve

Probe

Pin"

is

checked

in

the

Designer software, PRA and PRB pins are reserved as

dedicated outputs for probing. If PRA and PRB pins are

required as user I/Os to achieve successful layout and

"Reserve Probe Pin" is checked, the layout tool will

override the option and place user I/Os on PRA and PRB

pins.

CEQM = Equivalent capacitance of logic modules in pF

CEQI = Equivalent capacitance of input buffers in pF

CEQO = Equivalent capacitance of output buffers in pF

CEQCR = Equivalent capacitance of routed array clock in

pF

CL

= Output load capacitance in pF

fm

= Average logic module switching rate in MHz

fn

= Average input buffer switching rate in MHz

fp

= Average output buffer switching rate in MHz

fq1

= Average first routed array clock rate in MHz

fq2

= Average second routed array clock rate in MHz

Device Type

r1

routed_Clk1

r2

routed_Clk2

A40MX02

41.4

N/A

A40MX04

68.6

N/A

A42MX09

118

A42MX16

165

A42MX24

185

A42MX36

220

Figure 1-12 Silicon Explorer II Setup with 40MX

40MX

Silicon

Explorer II

PRA

PRB

SDO

DCLK

SDI

MODE

Serial Connection

to Windows PC

16 Logic Analyzer Channels

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A40MX04-PL44IX79 | FPGA, 547 CLBS, 6000 GATES, 80 MHz, PQCC44 |

| A40MX04-PL44I | FPGA, 547 CLBS, 6000 GATES, 80 MHz, PQCC44 |

| A40MX04-PL44MX79 | FPGA, 547 CLBS, 6000 GATES, 80 MHz, PQCC44 |

| A40MX04-PL44M | FPGA, 547 CLBS, 6000 GATES, 80 MHz, PQCC44 |

| A40MX04-PL44X79 | FPGA, 547 CLBS, 6000 GATES, 80 MHz, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A40MX04-FVQ80I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A40MX04-FVQ80M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A40MX04-FVQG80 | 功能描述:IC FPGA MX SGL CHIP 6K 80-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:MX 標(biāo)準(zhǔn)包裝:152 系列:IGLOO PLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):792 RAM 位總計(jì):- 輸入/輸出數(shù):120 門數(shù):30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應(yīng)商設(shè)備封裝:289-CSP(14x14) |

| A40MX04-PL100 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:40MX and 42MX FPGA Families |

| A40MX04-PL100ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:40MX and 42MX FPGA Families |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。