- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄362031 > A54SX08-3TQ144 Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號(hào): | A54SX08-3TQ144 |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA) |

| 文件頁(yè)數(shù): | 15/36頁(yè) |

| 文件大小: | 833K |

| 代理商: | A54SX08-3TQ144 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

v2.0

15

54SX Family FPGAs RadTolerant and HiRel

Temperature and Voltage Derating Factors

(Normalized to Worst-Case Commercial, T

J

= 70

°

C, V

CCA

= 3.0V)

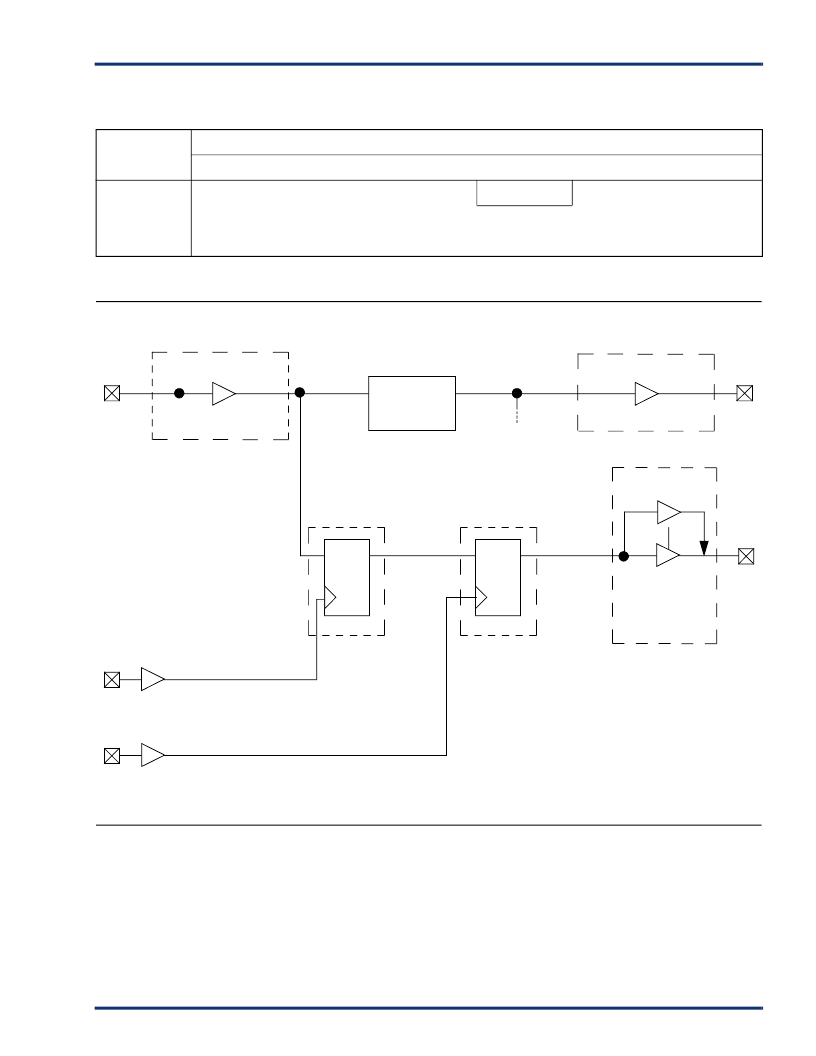

54SX Timing Model*

Hard-Wired Clock

External Set-Up = t

INY

+ t

IRD1

+ t

SUD

–

t

HCKH

= 2.2 + 0.7 + 0.8

–

1.7 = 2.0 ns

Clock-to-Out (Pin-to-Pin)

= t

HCKH

+ t

RCO

+ t

RD1

+ t

DHL

= 1.7 + 0.6 + 0.7 + 2.8 = 5.8 ns

Routed Clock

External Set-Up = t

INY

+ t

IRD1

+ t

SUD

–

t

RCKH

= 2.2 + 0.7 + 0.8

–

2.4 = 1.3 ns

Clock-to-Out (Pin-to-Pin)

= t

RCKH

+ t

RCO

+ t

RD1

+ t

DHL

= 2.4 + 0.6 + 0.7 + 2.8 = 6.5 ns

V

CCA

Junction Temperature (T

J

)

–

40

0

25

70

85

125

3.0

0.78

0.87

0.89

1.00

1.04

1.16

3.3

0.73

0.82

0.83

0.93

0.97

1.08

3.6

0.69

0.77

0.78

0.87

0.92

1.02

*Values shown for A54SX16-1 at worst-case commercial conditions.

Output Delays

Internal Delays

Input Delays

Hard-Wired

Clock

I/O Module

F

HMAX

= 240 MHz

t

INY

= 2.2 ns

t

IRD2

= 1.2 ns

Combinatorial

Cell

t

PD

=0.9 ns

Register

Cell

I/O Module

t

RD1

= 0.7 ns

t

RD4

= 2.2 ns

t

RD8

= 4.3 ns

t

DHL

= 2.8 ns

I/O Module

Routed

Clock

F

MAX

= 175 MHz

D

Q

D

Q

t

DHL

= 2.8 ns

t

ENZH

= 2.8 ns

t

RD1

= 0.7 ns

t

RCO

= 0.6 ns

t

SUD

= 0.8 ns

HD

= 0.0 ns

Predicted

Routing

Delays

t

RCKH

= 2.8 ns (100% Load)

t

RD1

= 0.7 ns

Register

Cell

t

RCO

= 0.6 ns

t

HCKH

= 1.3 ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A54SX08-3TQ176 | Field Programmable Gate Array (FPGA) |

| A54SX08-3VQ100 | Field Programmable Gate Array (FPGA) |

| A54SX08A1FG144M | Logic IC |

| A54SX08AFG144 | Logic IC |

| A54SX08AFG144I | Logic IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A54SX08-3TQ176 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| A54SX08-3TQ208 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:54SX Family FPGAs |

| A54SX08-3TQ208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:54SX Family FPGAs |

| A54SX08-3TQ208M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:54SX Family FPGAs |

| A54SX08-3TQ208PP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:54SX Family FPGAs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。