- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379533 > A54SX08P-3VQ208 (Electronic Theatre Controls, Inc.) 54SX Family FPGAs PDF資料下載

參數(shù)資料

| 型號: | A54SX08P-3VQ208 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | FPGA |

| 英文描述: | 54SX Family FPGAs |

| 中文描述: | 54SX家庭的FPGA |

| 文件頁數(shù): | 5/57頁 |

| 文件大小: | 415K |

| 代理商: | A54SX08P-3VQ208 |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

v3.1

5

5 4 S X F a m ily F P G A s

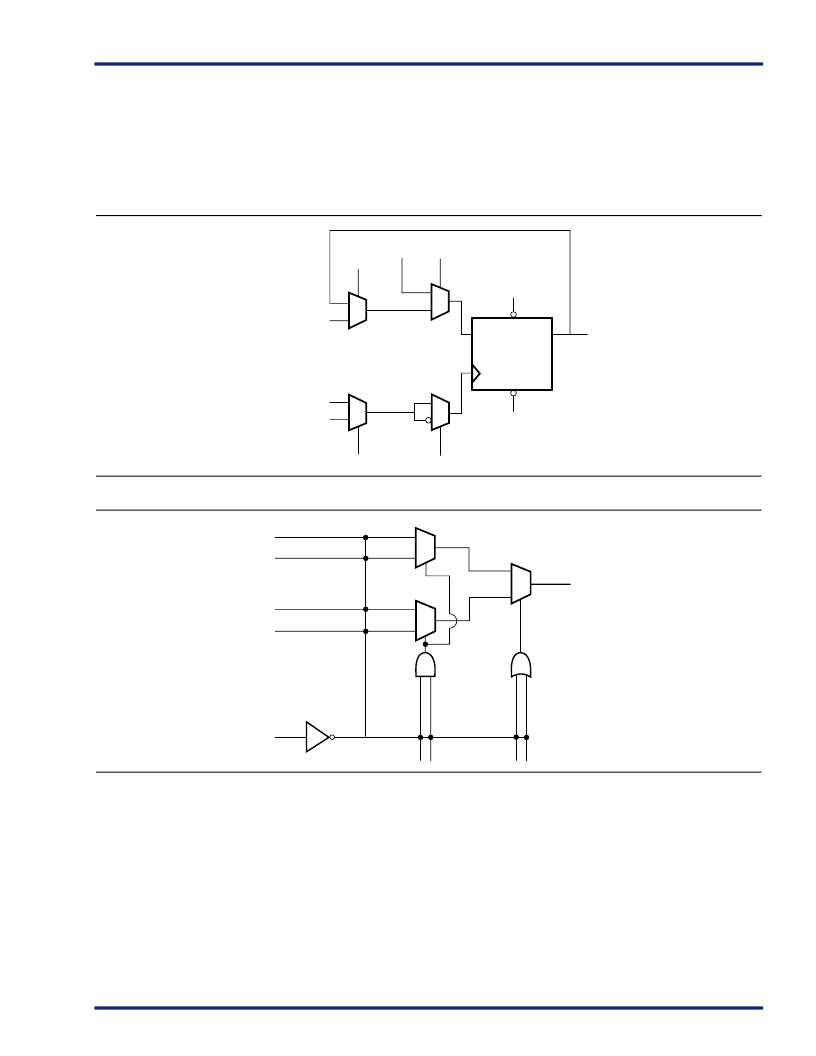

The C-cell implements a range of combinatorial functions

up to 5-inputs (

Figure3

). Inclusion of the DB input and its

associated inverter function dramatically increases the

number of combinatorial functions that can be

implemented in a single module from 800 options in

previous architectures to more than 4,000 in the SX

architecture. An example of the improved flexibility

enabled by the inversion capability is the ability to integrate

a 3-input exclusive-OR function into a single C-cell. This

facilitates construction of 9-bit parity-tree functions with 2

ns propagation delays. At the same time, the C-cell

structure is extremely synthesis friendly, simplifying the

overall design and reducing synthesis time.

C hip A rc hit e c t ure

The SX family’s chip architecture provides a unique

approach to module organization and chip routing that

delivers the best register/logic mix for a wide variety of new

and emerging applications.

Module Org a niz a t ion

Actel has arranged all C-cell and R-cell logic modules into

horizontal banks called

Clusters

. There are two types of

Clusters: Type 1 contains two C-cells and one R-cell, while

Type 2 contains one C-cell and two R-cells.

To increase design efficiency and device performance, Actel

has further organized these modules into

SuperClusters

(

Figure4 on page6

). SuperCluster 1 is a two-wide grouping

of Type 1 clusters. SuperCluster 2 is a two-wide group

containing one Type 1 cluster and one Type 2 cluster. SX

devices feature more SuperCluster 1 modules than

SuperCluster 2 modules because designers typically require

significantly more combinatorial logic than flip-flops.

Figure 2

R-Cell

Figure 3

C-Cell

Direct

Connect

Input

CLKA,

CLKB,

Internal Logic

HCLK

CKS

CKP

CLRB

PSETB

Y

D

Q

Routed

Data Input

S0

S1

D0

D1

D2

D3

DB

A0

B0

A1

B1

Sa

Sb

Y

相關PDF資料 |

PDF描述 |

|---|---|

| A54SX16 | Quad 2-input positive-NAND gates 14-SO 0 to 70 |

| A54SX32 | Quad 2-input positive-NAND gates 8-SO 0 to 70 |

| A54SX32-1BG208I | Quad 2-input positive-NAND gates 8-SO 0 to 70 |

| A54SX32-1BG208M | Quad 2-input positive-NAND gates 8-SO 0 to 70 |

| A54SX32-1FG208M | 54SX Family FPGAs |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| A54SX08P-3VQ208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:54SX Family FPGAs |

| A54SX08P-3VQ208M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:54SX Family FPGAs |

| A54SX08P-3VQ208PP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:54SX Family FPGAs |

| A54SX08P-3VQG208 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:SX Family FPGAs |

| A54SX08-P-3VQG208I | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:SX Family FPGAs |

發(fā)布緊急采購,3分鐘左右您將得到回復。