- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄362029 > A54SX16-CQ256M Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號(hào): | A54SX16-CQ256M |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA) |

| 文件頁(yè)數(shù): | 10/36頁(yè) |

| 文件大小: | 833K |

| 代理商: | A54SX16-CQ256M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

54SX Family FPGAs RadTolerant and HiRel

10

v2.0

machine reaches the

“

logic reset

”

state. At this point the

BST pins will be released and will function as regular I/O

pins. The "logic reset

”

state is reached 5 TCK cycles after

the TMS pin is set to logical HIGH.

The program fuse determines whether the device is in

Dedicated Test or Flexible mode. The default (fuse not

programmed) is Flexible mode.

Development Tool Support

The RT54SX RadTolerant devices are fully supported by

Actel

’

s line of FPGA development tools, including the Actel

DeskTOP Series and Designer Series

’

tools. The Actel

DeskTOP Series is an integrated design environment for PCs

that includes design entry, simulation, synthesis, and

place-and-route tools. Designer Series is Actel

’

s suite of

FPGA development point tools for PCs and Workstations

that includes the ACTgen Macro Builder, Designer Series

with DirectTime timing driven place-and-route and analysis

tools, and device programming software.

RT54SX Probe Circuit Control Pins

The RT54SX RadTolerant devices contain internal probing

circuitry that provides built-in access to every node in a

design, enabling 100-percent real-time observation and

analysis of a device's internal logic nodes without design

iteration. The probe circuitry is accessed by Silicon Explorer

II, an easy to use integrated verification and logic analysis

tool that can sample data at 100 MHz (asynchronous) or

66 MHz (synchronous). Silicon Explorer attaches to a PC

’

s

standard COM port, turning the PC into a fully functional 18

channel logic analyzer. Silicon Explorer allows designers to

complete the design verification process at their desks and

reduces verification time from several hours per cycle to a

few seconds.

The Silicon Explorer II tool uses the boundary scan ports

(TDI, TRST, TCK, TMS, and TDO) to select the desired nets

for verification. The selected internal nets are assigned to

the PRA/PRB pins for observation.

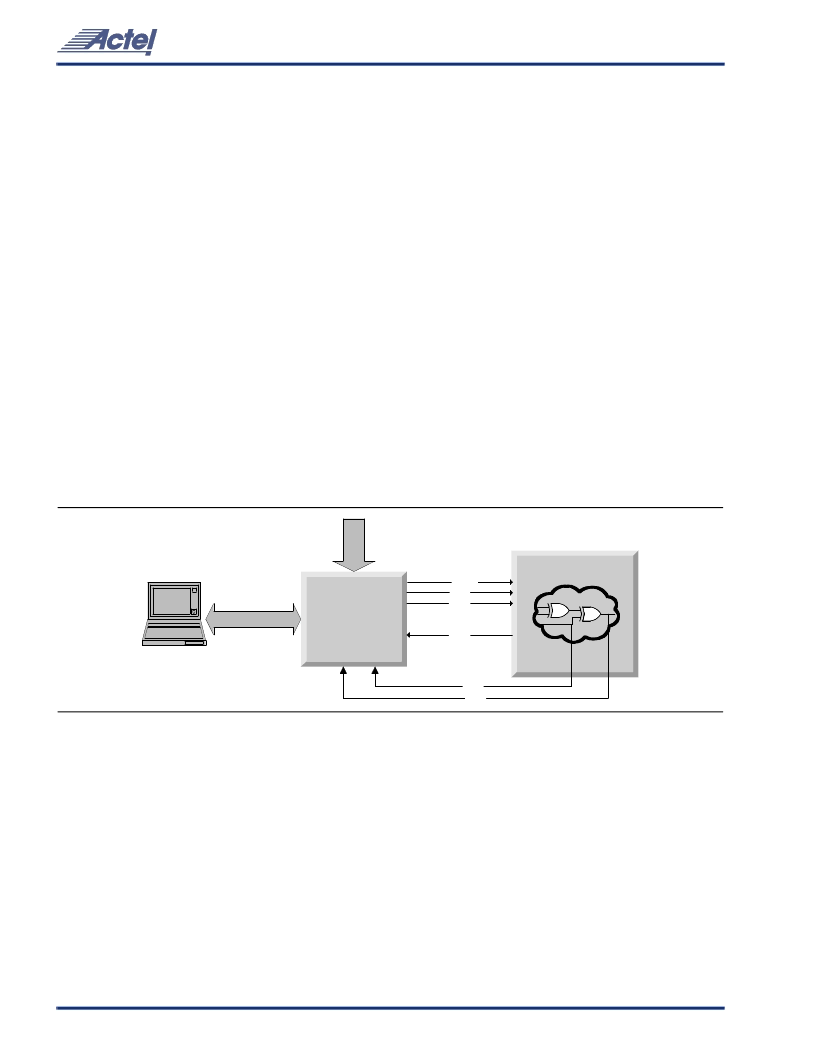

Figure 11

illustrates the

interconnection between Silicon Explorer II and the FPGA

to perform in-circuit verification.

Design Considerations

For prototyping, the TDI, TCK, TDO, PRA, and PRB pins

should not be used as input or bidirectional ports. Because

these pins are active during probing, critical signals input

through these pins are not available while probing. In

addition, the security fuse should not be programmed during

prototyping because doing so disables the probe circuitry.

Figure 11

Probe Setup

Silicon Explorer II

TCK

TMS

TDO

PRA

PRB

Serial Connection

1

C

RT54SX-S FPGA

TRST

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A54SX16P-1TQ144 | Field Programmable Gate Array (FPGA) |

| A54SX16P-1TQ144I | Field Programmable Gate Array (FPGA) |

| A54SX16P-1TQ144M | Field Programmable Gate Array (FPGA) |

| A54SX16P-1TQ176 | Field Programmable Gate Array (FPGA) |

| A54SX16P-1TQ176I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A54SX16P-1PQ208 | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:SX 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門(mén)數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A54SX16P-1PQ208I | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:SX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

| A54SX16P-1PQ208M | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:SX 標(biāo)準(zhǔn)包裝:1 系列:ProASICPLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計(jì):129024 輸入/輸出數(shù):248 門(mén)數(shù):600000 電源電壓:2.3 V ~ 2.7 V 安裝類(lèi)型:表面貼裝 工作溫度:- 封裝/外殼:352-BFCQFP,帶拉桿 供應(yīng)商設(shè)備封裝:352-CQFP(75x75) |

| A54SX16P-1PQG208 | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:是 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:SX 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門(mén)數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A54SX16P-1PQG208I | 功能描述:IC FPGA SX 24K GATES 208-PQFP RoHS:是 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:SX 產(chǎn)品培訓(xùn)模塊:Three Reasons to Use FPGA's in Industrial Designs Cyclone IV FPGA Family Overview 特色產(chǎn)品:Cyclone? IV FPGAs 標(biāo)準(zhǔn)包裝:60 系列:CYCLONE® IV GX LAB/CLB數(shù):9360 邏輯元件/單元數(shù):149760 RAM 位總計(jì):6635520 輸入/輸出數(shù):270 門(mén)數(shù):- 電源電壓:1.16 V ~ 1.24 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FBGA(23x23) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。