- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄4455 > A54SX32A-1PQG208 (Microsemi SoC)IC FPGA SX 48K GATES 208-PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | A54SX32A-1PQG208 |

| 廠商: | Microsemi SoC |

| 文件頁(yè)數(shù): | 98/108頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA SX 48K GATES 208-PQFP |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | SX-A |

| LAB/CLB數(shù): | 2880 |

| 輸入/輸出數(shù): | 174 |

| 門(mén)數(shù): | 48000 |

| 電源電壓: | 2.25 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)當(dāng)前第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)

SX-A Family FPGAs

v5.3

1-5

Clock Resources

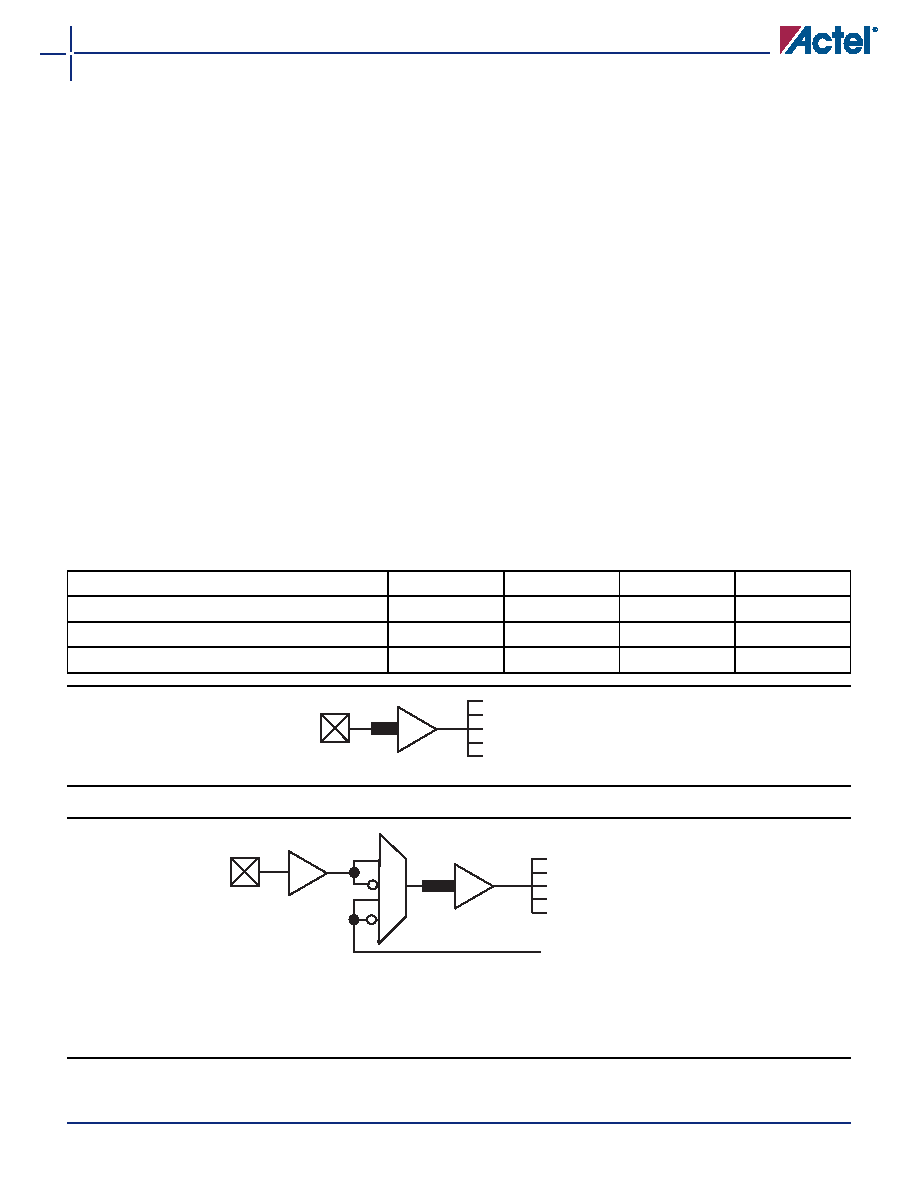

Actel’s high-drive routing structure provides three clock

networks (Table 1-1). The first clock, called HCLK, is

hardwired from the HCLK buffer to the clock select

multiplexor (MUX) in each R-cell. HCLK cannot be

connected to combinatorial logic. This provides a fast

propagation path for the clock signal. If not used, this

pin must be set as Low or High on the board. It must not

be left floating. Figure 1-7 describes the clock circuit

used for the constant load HCLK and the macros

supported.

HCLK does not function until the fourth clock cycle each

time the device is powered up to prevent false output

levels due to any possible slow power-on-reset signal and

fast start-up clock circuit. To activate HCLK from the first

cycle, the TRST pin must be reserved in the Design

software and the pin must be tied to GND on the board.

Two additional clocks (CLKA, CLKB) are global clocks that

can be sourced from external pins or from internal logic

signals within the SX-A device. CLKA and CLKB may be

connected to sequential cells or to combinational logic. If

CLKA or CLKB pins are not used or sourced from signals,

these pins must be set as Low or High on the board. They

must not be left floating. Figure 1-8 describes the CLKA

and CLKB circuit used and the macros supported in SX-A

devices with the exception of A54SX72A.

In

addition,

the

A54SX72A

device

provides

four

quadrant clocks (QCLKA, QCLKB, QCLKC, and QCLKD—

corresponding to bottom-left, bottom-right, top-left,

and top-right locations on the die, respectively), which

can be sourced from external pins or from internal logic

signals within the device. Each of these clocks can

individually drive up to an entire quadrant of the chip,

or they can be grouped together to drive multiple

quadrants (Figure 1-9 on page 1-6). QCLK pins can

function as user I/O pins. If not used, the QCLK pins

must be tied Low or High on the board and must not be

left floating.

For more information on how to use quadrant clocks in

the A54SX72A device, refer to the Global Clock Networks

RT54SX72S Quadrant Clocks application notes.

The CLKA, CLKB, and QCLK circuits for A54SX72A as well

as the macros supported are shown in Figure 1-10 on

page 1-6. Note that bidirectional clock buffers are only

available in A54SX72A. For more information, refer to

Table 1-1 SX-A Clock Resources

A54SX08A

A54SX16A

A54SX32A

A54SX72A

Routed Clocks (CLKA, CLKB)

2

Hardwired Clocks (HCLK)

1

Quadrant Clocks (QCLKA, QCLKB, QCLKC, QCLKD)

0

4

Figure 1-7 SX-A HCLK Clock Buffer

Figure 1-8 SX-A Routed Clock Buffer

Constant Load

Clock Network

HCLKBUF

Clock Network

From Internal Logic

CLKBUF

CLKBUFI

CLKINT

CLKINTI

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMM43DRYF | CONN EDGECARD 86POS DIP .156 SLD |

| AMM28DSES | CONN EDGECARD 56POS .156 EYELET |

| EP4CGX30CF19I7N | IC CYCLONE IV GX FPGA 30K 324FBG |

| 5748678-5 | CONN BACKSHELL DB50 PLASTIC BLCK |

| AMM28DRTS | CONN EDGECARD 56POS DIP .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A54SX32A-1PQG208I | 功能描述:IC FPGA SX 48K GATES 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:SX-A 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門(mén)數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A54SX32A-1PQG208M | 制造商:Microsemi Corporation 功能描述:FPGA SX-A 32K GATES 1800 CELLS 278MHZ 0.25UM/0.22UM 2.5V 208 - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA 174 I/O 208PQFP |

| A54SX32A-1TQ100 | 功能描述:IC FPGA SX 48K GATES 100-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:SX-A 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門(mén)數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A54SX32A-1TQ100I | 功能描述:IC FPGA SX 48K GATES 100-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:SX-A 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門(mén)數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| A54SX32A-1TQ100M | 制造商:Microsemi Corporation 功能描述:FPGA SX-A 32K GATES 1800 CELLS 278MHZ 0.25UM/0.22UM 2.5V 100 - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA 48K GATES 100TQFP 制造商:Microsemi Corporation 功能描述:IC FPGA 81 I/O 100TQFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。