- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362073 > ACT-F128K8N-150F7C EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | ACT-F128K8N-150F7C |

| 元件分類: | EEPROM |

| 英文描述: | EEPROM |

| 中文描述: | EEPROM的 |

| 文件頁數(shù): | 5/21頁 |

| 文件大小: | 153K |

| 代理商: | ACT-F128K8N-150F7C |

Aeroflex Circuit Technology

SCD1676 REV A 5/6/98 Plainview NY (516) 694-6700

5

Device Operation

The ACT-F128K8 Monolithic module is composed of one,

1 megabit flash EEPROM.

Programming of the ACT-F128K8 is accomplished by

executing the program command sequence. The

program algorithm, which is an internal algorithm,

automatically times the program pulse widths and

verifies proper cell status. Sectors can be programed

and verified in less than 0.3 second. Erase is

accomplished by executing the erase command

sequence. The erase algorithm, which is internal,

automatically preprograms the array if it is not already

programed before executing the erase operation. During

erase, the device automatically times the erase pulse

widths and verifies proper cell status. The entire

memory is typically erased and verified in 3 seconds

(if pre-programmed). The sector mode allows for 16K

byte blocks of memory to be erased and reprogrammed

without affecting other blocks.

Bus Operation

READ

The ACT-F128K8 has two control functions, both of

which must be logically active, to obtain data at the

outputs. Chip Enable (CE) is the power control and

should be used for device selection. Output-Enable (OE)

is the output control and should be used to gate data to

the output pins of the chip selected. Figure 7 illustrates

AC read timing waveforms.

OUTPUT DISABLE

With Output-Enable at a logic high level (V

IH

), output

from the device is disabled. Output pins are placed in a

high impedance state.

STANDBY MODE

The ACT-F128K8 has two standby modes, a CMOS

standby mode (CE input held at Vcc + 0.5V), where the

current consumed is typically less than 400 μA; and a

TTL standby mode (CE is held V

IH

) is approximately 1

mA. In the standby mode the outputs are in a high

impedance state, independent of the OE input.

If the device is deselected during erasure or

programming, the device will draw active current until the

operation is completed.

WRITE

Device erasure and programming are accomplished via

the command register. The contents of the register

serve as input to the internal state machine. The state

machine outputs dictate the function of the device.

The command register itself does not occupy an

addressable memory location. The register is a latch

used to store the command, along with address and data

information needed to execute the command. The

command register is written by bringing WE to a logic

low level (V

IL

), while CE is low and OE is at V

IH

.

Addresses are latched on the falling edge of WE or CE,

whichever happens later. Data is latched on the rising

edge of the WE or CE whichever occurs first. Standard

microprocessor write timings are used. Refer to AC

Program Characteristics and Waveforms, Figures 3,

8 and 13.

Command Definitions

Device operations are selected by writing specific

address and data sequences into the command register.

Table 3 defines these register command sequences.

READ/RESET COMMAND

The read or reset operation is initiated by writing the

read/reset command sequence into the command

register. Microprocessor read cycles retrieve array data

from the memory. The device remains enabled for reads

until the command register contents are altered.

The device will automatically power-up in the read/reset

state. In this case, a command sequence is not required

to read data. Standard microprocessor read cycles will

retrieve array data. The device will automatically

power-up in the read/reset state. In this case, a

command sequence is not required to read data.

Standard Microprocessor read cycles will retrieve array

data. This default value ensures that no spurious

alteration of the memory content occurs during the

power transition. Refer to the AC Read Characteristics

and Figure 7 for the specific timing parameters.

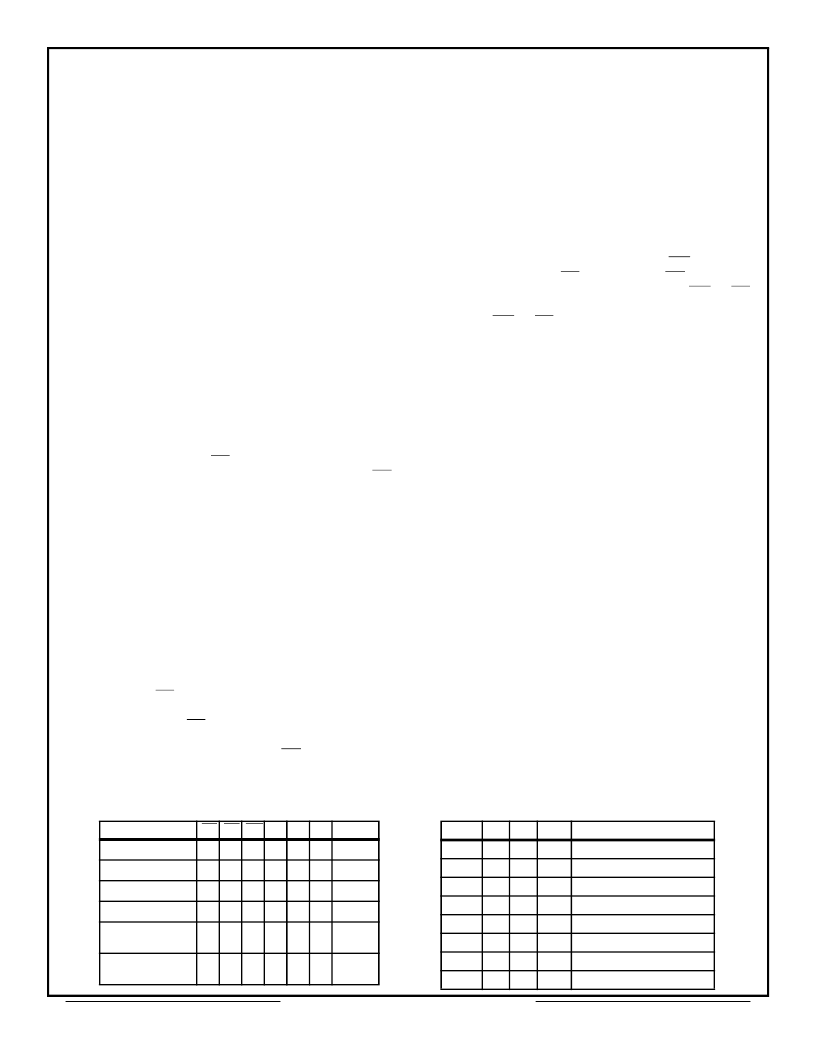

Table 1 – Bus Operations

Operation

CE OE WE A0 A1 A9

I/O

READ

L

L

H

A

0

A

1

A

9

DOUT

STANDBY

H

X

X

X

X

X

HIGH Z

OUTPUT DISABLE

L

H

H

X

X

X

HIGH Z

WRITE

L

H

L

A

0

A

1

A

9

D

IN

ENABLE SECTOR

PROTECT

L

V

ID

L

X

X

V

ID

X

VERIFY SECTOR

PROTECT

L

L

H

L

H

V

ID

Code

Table 2 – Sector Addresses Table

A16 A15

A14

Address Range

SA0

0

0

0

00000h – 03FFFh

SA1

0

0

1

04000h – 07FFFh

SA2

0

1

0

08000h – 0BFFFh

SA3

0

1

1

0C000h – 0FFFFh

SA4

1

0

0

10000h – 13FFFh

SA5

1

0

1

14000h – 17FFFh

SA6

1

1

0

18000h – 1BFFFh

SA7

1

1

1

1C000h – 1FFFFh

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACT-F128K8N-150F7I | EEPROM |

| ACT-F128K8N-150F7M | EEPROM |

| ACT-F128K8N-150F7Q | EEPROM |

| ACT-F128K8N-150F7T | EEPROM |

| ACT-F128K8N-150P4C | EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACT-F128K8N-150F7I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| ACT-F128K8N-150F7M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| ACT-F128K8N-150F7Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| ACT-F128K8N-150F7T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| ACT-F128K8N-150P4C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。