- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378274 > ACTS630D (Intersil Corporation) Radiation Hardened EDAC (Error Detection and Correction) PDF資料下載

參數(shù)資料

| 型號(hào): | ACTS630D |

| 廠商: | Intersil Corporation |

| 英文描述: | Radiation Hardened EDAC (Error Detection and Correction) |

| 中文描述: | 輻射加固經(jīng)發(fā)會(huì)(錯(cuò)誤檢測和校正) |

| 文件頁數(shù): | 1/4頁 |

| 文件大?。?/td> | 489K |

| 代理商: | ACTS630D |

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

|

Copyright

Intersil Corporation 1999

ACTS630MS

Radiation Hardened EDAC

(Error Detection and Correction)

Features

Devices QML Qualified in Accordance with MIL-PRF-38535

Detailed Electrical and Screening Requirements are Contained in

SMD# 5962-96721 and Intersil’s QM Plan

1.25 Micron Radiation Hardened SOS CMOS

Total Dose . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . >300K RAD (Si)

Single Event Upset (SEU) Immunity: <1 x 10

-10

Errors/Bit/Day

(Typ)

SEU LET Threshold . . . . . . . . . . . . . . . . . . . . . . . >100 MEV-cm

2

/mg

Dose Rate Upset . . . . . . . . . . . . . . . . >10

11

RAD (Si)/s, 20ns Pulse

Dose Rate Survivability. . . . . . . . . . . >10

12

RAD (Si)/s, 20ns Pulse

Latch-Up Free Under Any Conditions

Military Temperature Range . . . . . . . . . . . . . . . . . .-55

o

C to +125

o

C

Significant Power Reduction Compared to ALSTTL Logic

DC Operating Voltage Range . . . . . . . . . . . . . . . . . . . . 4.5V to 5.5V

Input Logic Levels

- VIL = 0.8V Max

- VIH = VCC/2 Min

Input Current

≤

1

μ

A at VOL, VOH

Fast Propagation Delay. . . . . . . . . . . . . . . . 37ns (Max), 24ns (Typ)

Description

The Intersil ACTS630MS is a Radiation Hardened 16-bit parallel error

detection and correction circuit. It uses a modified Hamming code to

generate a 6-bit check word from each 16-bit data word. The check word

is stored with the data word during a memory write cycle; during a

memory read cycle a 22-bit word is taken form memory and checked for

errors. Single bit errors in the data words are flagged and corrected. Sin-

gle bit errors in check words are flagged but not corrected. The position

of the incorrect bit is pinpointed, in both cases, by the 6-bit error

syndrome code which is output during the error correction cycle.

The ACTS630MS utilizes advanced CMOS/SOS technology to achieve

high-speed operation. This device is a member of a radiation hardened,

high-speed, CMOS/SOS Logic Family.

The ACTS630MS is supplied in a 28 lead Ceramic Flatpack (K suffix) or

a 28 Lead Ceramic Dual-In-Line Package (D suffix).

January 1996

Ordering Information

PART NUMBER

TEMPERATURE RANGE

SCREENING LEVEL

PACKAGE

5962F9672101VXC

-55

o

C to +125

o

C

MIL-PRF-38535 Class V

28 Lead SBDIP

5962F9672101VYC

-55

o

C to +125

o

C

MIL-PRF-38535 Class V

28 Lead Ceramic Flatpack

ACTS630D/Sample

25

o

C

Sample

28 Lead SBDIP

ACTS630K/Sample

25

o

C

Sample

28 Lead Ceramic Flatpack

ACTS630HMSR

25

o

C

Die

Die

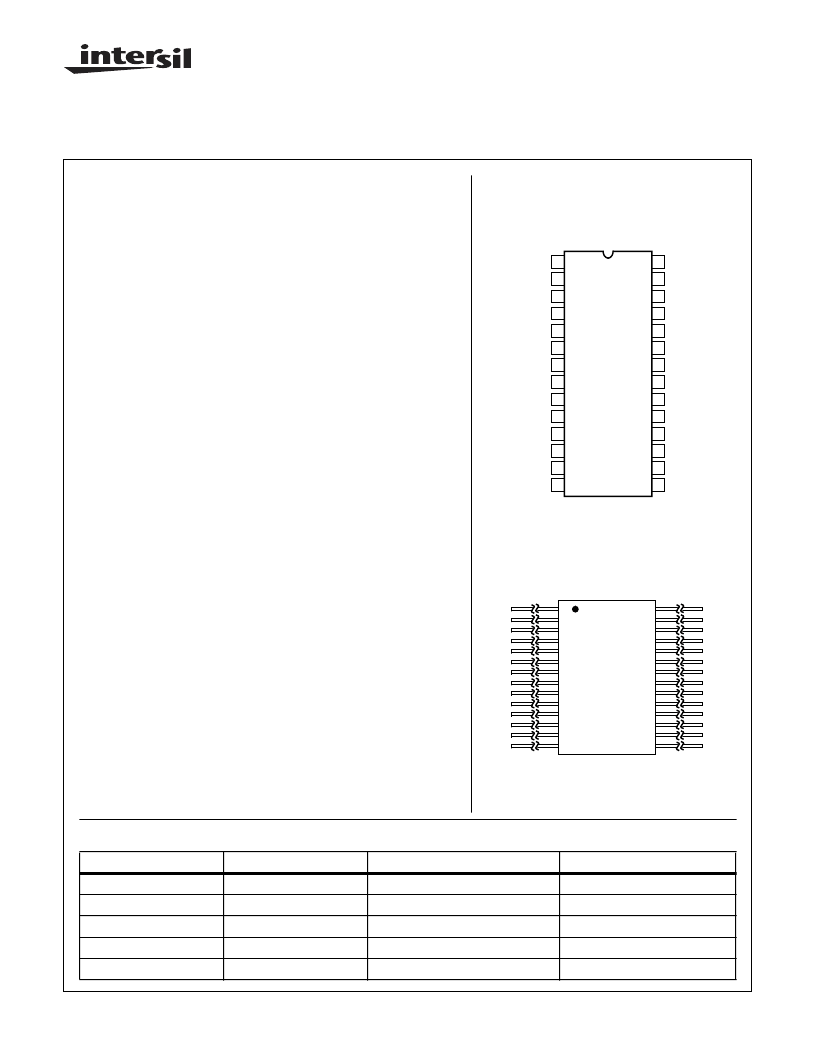

Pinouts

28 PIN CERAMIC DUAL-IN-LINE, MIL-STD-1835

DESIGNATOR CDIP-T28, LEAD FINISH C

TOP VIEW

28 PIN CERAMIC FLATPACK, MIL-STD-1835

DESIGNATOR CDFP3-F28, LEAD FINISH C

TOP VIEW

DEF

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

DB9

DB10

DB11

GND

VCC

S1

S0

CB0

CB1

CB3

CB5

DB15

DB14

DB13

DB12

SEF

CB2

CB4

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

DEF

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

DB9

DB10

DB11

GND

VCC

SEF

S1

S0

CB0

CB1

CB2

CB3

CB4

CB5

DB15

DB14

DB13

DB12

Spec Number

518786

File Number

3204.1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACTS630K | Radiation Hardened EDAC (Error Detection and Correction) |

| ACTS630MS | Radiation Hardened EDAC (Error Detection and Correction) |

| ACTS630HMSR | Radiation Hardened EDAC (Error Detection and Correction) |

| ACTS74D | Radiation Hardened Dual D Flip Flop with Set and Reset |

| ACTS74HMSR | Radiation Hardened Dual D Flip Flop with Set and Reset |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACTS630HMSR | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened EDAC (Error Detection and Correction) |

| ACTS630K | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened EDAC (Error Detection and Correction) |

| ACTS630MS | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened EDAC (Error Detection and Correction) |

| ACTS74D | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Radiation Hardened Dual D Flip Flop with Set and Reset |

| ACTS74DMSR-02 | 制造商:Intersil Corporation 功能描述:RAD HARD CMOS, DUAL D FLIP-FLOP, W/SET/RESET,TTL,DIE,CLASS V - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。