- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373859 > AD1816AJST (ANALOG DEVICES INC) SoundPort Controller PDF資料下載

參數(shù)資料

| 型號: | AD1816AJST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | SoundPort Controller |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁數(shù): | 17/52頁 |

| 文件大?。?/td> | 477K |

| 代理商: | AD1816AJST |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

AD1816A

–17–

REV. A

SE RIAL INT E RFACE S

I

2

S Serial Ports

T he two I

2

S serial ports on the AD1816A accept serial data in the following formats: Right-Justified, I

2

S-Justified and Left-Justified.

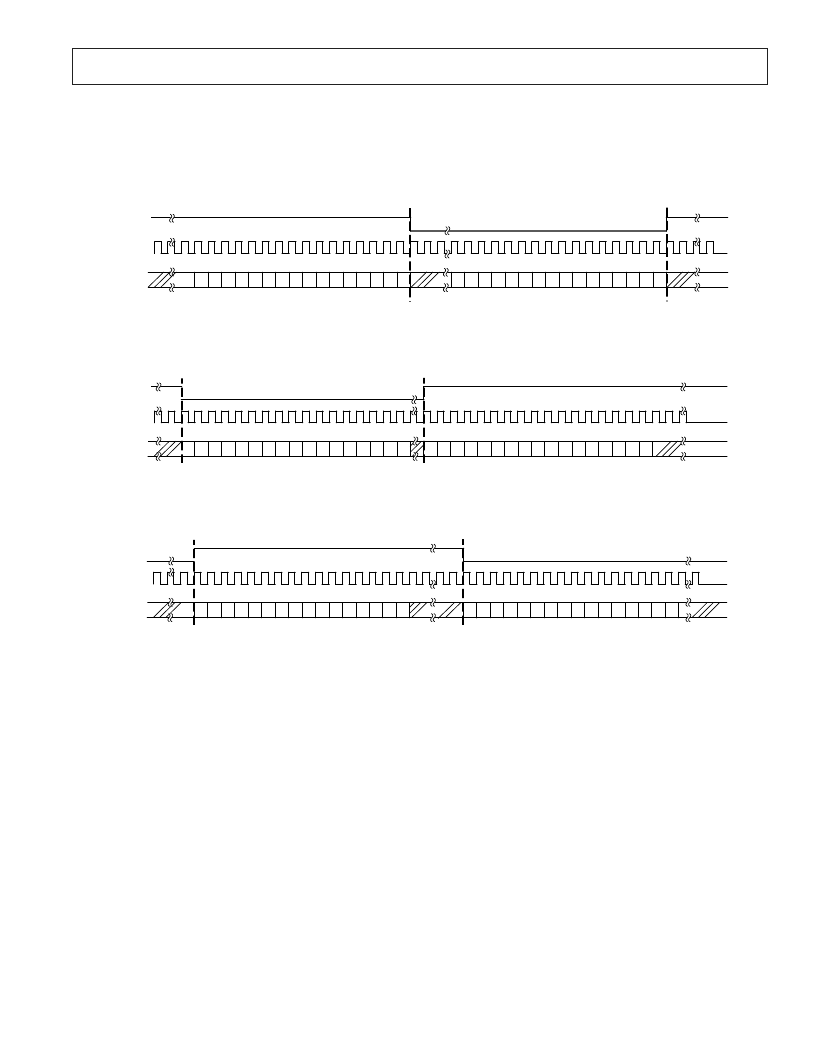

Figure 9 shows the right-justified mode. LRCLK is HI for the left channel and LO for the right channel. Data is valid on the rising

edge of the BCLK . T he MSB is delayed 16-bit clock periods from an LRCLK transition, so that when there are 64 BCLK periods

per LRCLK period, the LSB of the data will be right-justified to the next LRCLK transition.

14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

15

LRCLK

BCLK

SDATA

15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

LEFT CHANNEL

RIGHT CHANNEL

Figure 9. Serial Interface Right-J ustified Mode

Figure 10 shows the I

2

S-justified mode. LRCLK is LO for the left channel and HI for the right channel. Data is valid on the rising

edge of BCLK . T he MSB is left-justified to an LRCLK transition, but with a single BCLK period delay.

LRCLK

BCLK

SDATA

15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

LEFT CHANNEL

RIGHT CHANNEL

14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

15

Figure 10. Serial Interface I

2

S-J ustified Mode

Figure 11 shows the left-justified mode. LRCLK is HI for the left channel and LO for the right channel. Data is valid on the rising

edge of BCLK . T he MSB is left-justified to an LRCLK transition, with no MSB delay.

LRCLK

BCLK

SDATA

15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

LEFT CHANNEL

RIGHT CHANNEL

14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

15

Figure 11. Serial Interface Left-J ustified Mode

Bidirectional DSP Serial Interface

T he AD1816A SoundPort Controller transmits and receives both data and control/status information through its DSP serial interface

port (SPORT ). T he AD1816A is always the bus master and supplies the frame sync and the serial clock. T he AD1816A has four

pins assigned to the SPORT : SDI, SDO, SDFS and SCLK . T he SPORT has two operating modes: monitor and intercept. T he

SPORT always monitors the various data streams being processed by the AD1816A. In intercept mode, any of the digital data

streams can be manipulated by the DSP before reaching the final ADC or DAC stages.

T he SDI and SDO pins handle the serial data input and output of the AD1816A. Communication in and out of the AD1816A requires

that bits of data be transmitted after a rising edge of SCLK and sampled on the falling edge of SCLK . T he SCLK frequency is

always 11 MHz (or 1/3 or X T ALI).

DSP Serial Port Interface time slots are mapped as shown in T able I.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD1816A | SoundPort Controller(數(shù)字音頻的聲音端口控制器) |

| AD1818 | PCI SoundComm DC97 Digital Controller(PCI SoundComm DC97型數(shù)字控制器) |

| AD1819A | AC97 SoundPort Codec(AC97型聲音端口信號編解碼器) |

| AD1819BJST | AC’97 SoundPort Codec |

| AD1819 | ECONOLINE: RD & RC - Dual Output from a Single Input Rail- 1kVDC & 2kVDC Isolation- Power Sharing on Output- Custom Solutions Available- UL94V-0 Package Material- Efficiency to 86% |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ad1816js3 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| AD18-182 | 制造商:Thomas & Betts 功能描述:Terminal; 22 to 18 AWG; Brass; Non-Insulated; Tin Plated; UL 94V-2 制造商:Thomas & Betts 功能描述:DISCONNECTFEMALE 制造商:Thomas & Betts 功能描述:Quick Disconnect Terminal 18-22AWG F 21.08mm 5.84mm Tin |

| AD18-183 | 制造商:Thomas & Betts 功能描述:Terminal; 22 to 18 AWG; Brass; Nylon; Tin Plated; UL 94V-2 制造商:Thomas & Betts 功能描述:NON-INS FEM-187 DISC, 22-18 LEN .64 制造商:Thomas & Betts 功能描述:Quick Disconnect Terminal 18-22AWG F 16.26mm 5.84mm Tin |

| AD1819 | 制造商:AD 制造商全稱:Analog Devices 功能描述:AC’97 SoundPort Codec |

| AD1819AJST | 制造商:Rochester Electronics LLC 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。