- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373859 > AD1833AST (ANALOG DEVICES INC) Multichannel 24-Bit, 192 kHz, DAC PDF資料下載

參數(shù)資料

| 型號: | AD1833AST |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | DAC |

| 英文描述: | Multichannel 24-Bit, 192 kHz, DAC |

| 中文描述: | SERIAL INPUT LOADING, 24-BIT DAC, PQFP48 |

| 封裝: | PLASTIC, MS-026BBC, LQFP-48 |

| 文件頁數(shù): | 14/20頁 |

| 文件大小: | 419K |

| 代理商: | AD1833AST |

REV. 0

AD1833

–14–

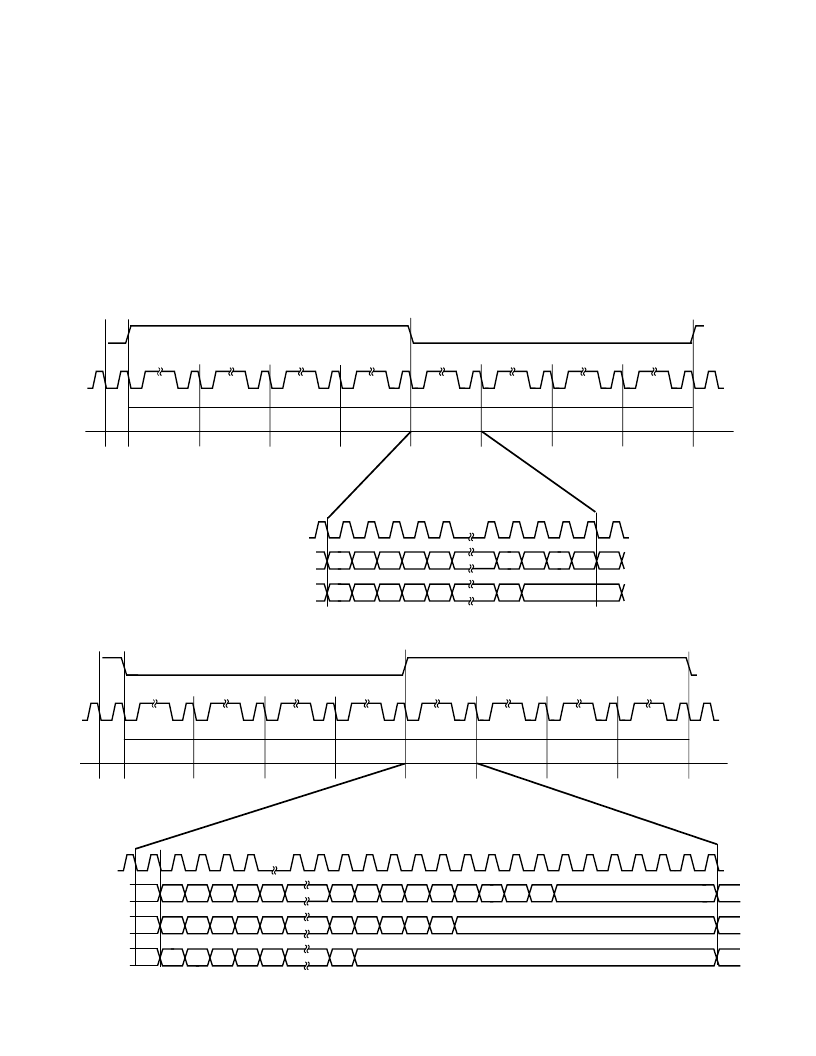

Packed Mode 128

In Packed Mode 128, all six data channels are “packed” into

one sample interval on one data pin. The BCLK runs at 128

×

f

S

; therefore there are 128 BCLK periods in each sample inter-

val. Each sample interval is broken into eight time slots, six slots

of 20 BCLKs and two of four BCLKs. The data length is restricted

in this mode to a maximum of 20 bits. The three left channels

are written first, MSB first, and the data is written on the falling

edge of BCLK. After the three left channels are written, there is

a space of four BCLKs and then the three right channels are

written. The L/

R

CLK defines the left and right data transmis-

sion; it is high for the three left channels and low for the three

right channels.

Packed Mode 256

In Packed Mode 256 all six data channels are “packed” into one

sample interval on one data pin. The BCLK runs at 256

×

f

S

;

therefore there are 256 BCLK periods in each sample interval.

Each sample interval is broken into eight time slots of 32 BCLKs

each. The data length can be 16, 20, or 24 bits. The three left

channels are written first, MSB first, and the data is written on

the falling edge of BCLK with a one BCLK period delay from

the start of the slot. After the three left channels are written,

there is a space of 32 BCLKs and then the three right channels

are written. The L/

R

CLK defines the left and right data trans-

mission; it is low for the three left channels and high for the

three right channels.

SLOT 1

LEFT 0

SLOT 2

LEFT 1

SLOT 3

LEFT 2

SLOT 4

RIGHT 0

SLOT 5

RIGHT 1

SLOT 6

RIGHT 2

L/

R

CLK

BCLK

DATA

MSB

24-BIT DATA

20-BIT DATA

16-BIT DATA

BCLK

–

1

–

2

–

3

–

4

+8

+7

+6

+5

+4

+3

+2

+1

LSB

MSB

–

1

–

2

–

3

–

4

+4

+3

+2

+1

LSB

MSB

–

1

–

2

–

3

–

4

LSB

Figure 10. Packed Mode 256

SLOT 1

LEFT 0

SLOT 2

LEFT 1

SLOT 3

LEFT 2

BLANK SLOT

4 SCLKs

SLOT 4

RIGHT 0

SLOT 5

RIGHT 1

SLOT 6

RIGHT 2

BLANK SLOT

4 SCLKs

MSB

20-BIT DATA

16-BIT DATA

BCLK

–

1

–

2

–

3

–

4

+4

+3

+2

+1

LSB

MSB

–

1

–

2

–

3

–

4

LSB

BCLK

DATA

L/

R

CLK

Figure 9. Packed Mode 128

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD1835 | 2 ADC, 8 DAC, 96 kHz, 24-Bit Codec |

| AD1835AS | 2 ADC, 8 DAC, 96 kHz, 24-Bit Codec |

| AD1836ACSRL | Multichannel 96 kHz Codec |

| AD1836AAS | Multichannel 96 kHz Codec |

| AD1836AASRL | Direct-Conversion TV Tuner |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD1833AST-REEL | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| AD1833CST | 制造商:Analog Devices 功能描述:DAC 6-CH Delta-Sigma 24-bit 48-Pin LQFP 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| AD1833CST-REEL | 制造商:Analog Devices 功能描述:DAC 6-CH Delta-Sigma 24-bit 48-Pin LQFP T/R 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| AD1835 | 制造商:AD 制造商全稱:Analog Devices 功能描述:2 ADC, 8 DAC, 96 kHz, 24-Bit Codec |

| AD1835A | 制造商:AD 制造商全稱:Analog Devices 功能描述:2 ADC, 8 DAC, 96 kHz, 24-Bit Codecs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。