- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373864 > AD1991ASV (ANALOG DEVICES INC) Class D/1-Bit Audio Power Output Stage PDF資料下載

參數(shù)資料

| 型號(hào): | AD1991ASV |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 音頻/視頻放大 |

| 英文描述: | Class D/1-Bit Audio Power Output Stage |

| 中文描述: | 20 W, 4 CHANNEL, AUDIO AMPLIFIER, PQFP52 |

| 封裝: | MS-026ACC, TQFP-52 |

| 文件頁(yè)數(shù): | 6/11頁(yè) |

| 文件大?。?/td> | 194K |

| 代理商: | AD1991ASV |

REV. 0

–6–

AD1991

FUNCTIONAL DESCRIPTION

Device Architecture

The AD1991 is an 8-transistor, audio, power output stage. The

AD1991 is arranged internally as four transistor pairs that can

be used as two H-bridge outputs (2-channel mode) or as four

single-ended outputs (4-channel mode), using either two or four

TTL compatible inputs to control the transistors. A dead time

is automatically provided between the switching of the high-

side transistor and low-side transistor when the control inputs

change level, to ensure that both the high-side transistor and

low-side transistor are never on at the same time.

Clock Source and Channel Mode Selection

When the AD1991 is brought out of reset, the logic levels on

MODE0 and MODE1 are latched internally. MODE0 determines

the internal state machine clock source. MODE1 determines the

channel mode and the function of

ERR0

(see Tables I and II.)

When the internal clock is used, the CLK pin should not be

connected.

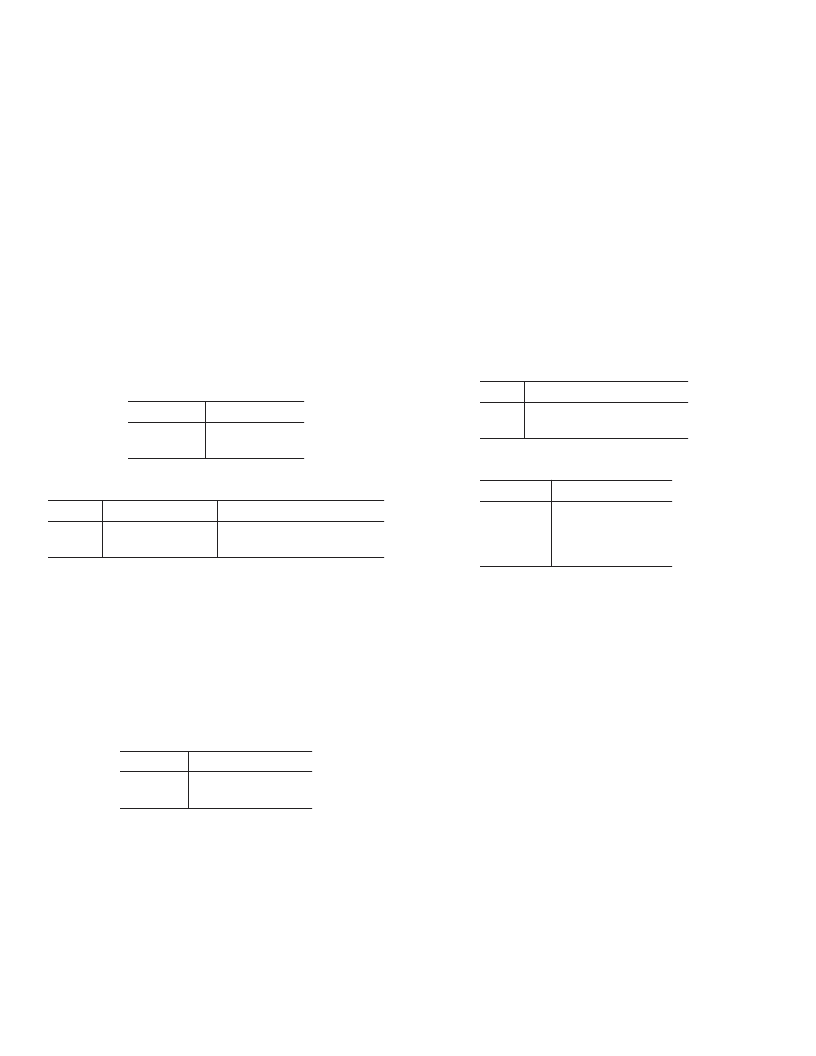

Table I. Clock Source Selection

MODE0

CLK Source

0

1

Internal

External

Table II. Channel Mode Selection

MODE1

Channel Mode

ERR0

Function

0

1

2-Channel Mode

4-Channel Mode

Data Loss Detection Output

Low-Side Disable Input

2-Channel Mode

Two loads are connected differentially—across OUTA and OUTB

and across OUTC and OUTD. Inputs INB and IND are unused

and should be tied to an appropriate dc voltage (see the Edge

Speed and Nonoverlap Settings section)

.

In this mode,

ERR0

is

an error output used to indicate data loss, which occurs when

there are no transitions on INA or INC for more than 50 ms.

This signal condition is hazardous in 2-channel mode because it

can cause a potentially large and harmful dc voltage across the

differential loads. Table III shows the input/output relationship.

Table III. Input/Output Relationship in 2-Channel Mode

Input

Controlled Output

INA

INC

OUTA, OUTB

OUTC, OUTD

4-Channel Mode

The 4-channel mode has two types of configuration: audio and

power supply. Neither of these configurations require data loss

detection. In the audio configuration, each single-ended load is

connected to the output through a blocking capacitor, which

prevents dc from reaching the load, thereby negating the need

for data loss detection. While in the power supply configuration,

it is desired to maintain a dc voltage on the load, also negating

the need for data loss detection. When used in the power supply

configuration, the four low-side transistors can also be disabled

and left permanently open if desired. This allows the loads to be

driven by switching only the high-side transistor on and off.

ERR0

is an input in 4-channel mode and is used to select

whether the four low-side transistors are enabled or disabled,

with 0 selecting disabled and 1 selecting enabled. Table IV

summarizes the function of

ERR0

in this mode. Table V shows

the input/output relationship.

Table IV.

ERR0

Function in 4-Channel Mode

ERR0

Low-Side Transistor Status

0

1

Disabled

Enabled

Table V. Input/Output Relationship in 4-Channel Mode

Input

Controlled Output

INA

INB

INC

IND

OUTA

OUTB

OUTC

OUTD

1-Channel Mode

One load is connected differentially—across OUTA and OUTC,

and OUTB and OUTD. This mono operation is established

by configuring the part for 2-channel mode and externally

connecting INA to INC, OUTA to OUTC, and OUTB to

OUTD (see Figure 4).

Thermal Protection

The AD1991 features thermal protection. When the die tempera-

ture exceeds approximately 135

°

C, the thermal warning error

output (

ERR2

) is asserted. If the die temperature exceeds

approximately 150

°

C, the thermal shutdown error output (

ERR3

)

is asserted. If this occurs, the part shuts down to prevent damage

to the part. When the die temperature drops below approximately

120

°

C, both error outputs de-assert and the part returns to nor-

mal operation.

Overcurrent Protection

The AD1991 features overcurrent or short-circuit protection. If

the current through any power transistors exceeds 5 A, the part

is muted and the overcurrent error output (

ERR1

) is asserted.

This is a latched error and does not clear automatically. To clear

the error condition and restore normal operation, the part must

be reset or

MUTE

must be asserted and de-asserted.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD1991 | Class D/1-Bit Audio Power Output Stage |

| AD1991ASVRL | Class D/1-Bit Audio Power Output Stage |

| AD1994ACPZRL | Audio Switching Amplifier |

| AD1994ACPZRL7 | Audio Switching Amplifier |

| AD203SN | Circular Connector; No. of Contacts:8; Series:LJTPQ00R; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:17; Circular Contact Gender:Socket; Circular Shell Style:Wall Mount Receptacle |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD1991ASVRL | 制造商:Analog Devices 功能描述:Audio Amp Speaker 1-CH Mono/2-CH Stereo/4-CH Stereo 40W Class-D 52-Pin TQFP T/R |

| AD1991ASVZ | 制造商:Analog Devices 功能描述:Audio Amp Speaker 1-CH Mono/2-CH Stereo/4-CH Stereo 40W Class-D 52-Pin TQFP 制造商:Analog Devices 功能描述:AUDIO POWER O/P STAGE CLASS D 1991 |

| AD1991ASVZRL | 制造商:Analog Devices 功能描述:Audio Amp Speaker 1-CH Mono/2-CH Stereo/4-CH Stereo 40W Class-D 52-Pin TQFP T/R |

| AD1992 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Audio Switching Amplifier |

| AD1992_06 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Audio Switching Amplifier |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。