- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373889 > AD6426XST (Analog Devices, Inc.) 1N5817 DIODE SCHOTTKY 20V 1A DO-41 PDF資料下載

參數(shù)資料

| 型號: | AD6426XST |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 1N5817 DIODE SCHOTTKY 20V 1A DO-41 |

| 中文描述: | 增強型手機處理器 |

| 文件頁數(shù): | 25/50頁 |

| 文件大?。?/td> | 506K |

| 代理商: | AD6426XST |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

Preliminary Technical Information

AD6426

This Information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no

obligation regarding future manufacture unless otherwise agreed to in writing. No responsibility is assumed by Analog Devices for its use; nor for any

infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent

rights of Analog Devices.

Revision Preliminary 2.3 (June 9, ′98)

- 25 -

Confidential Information

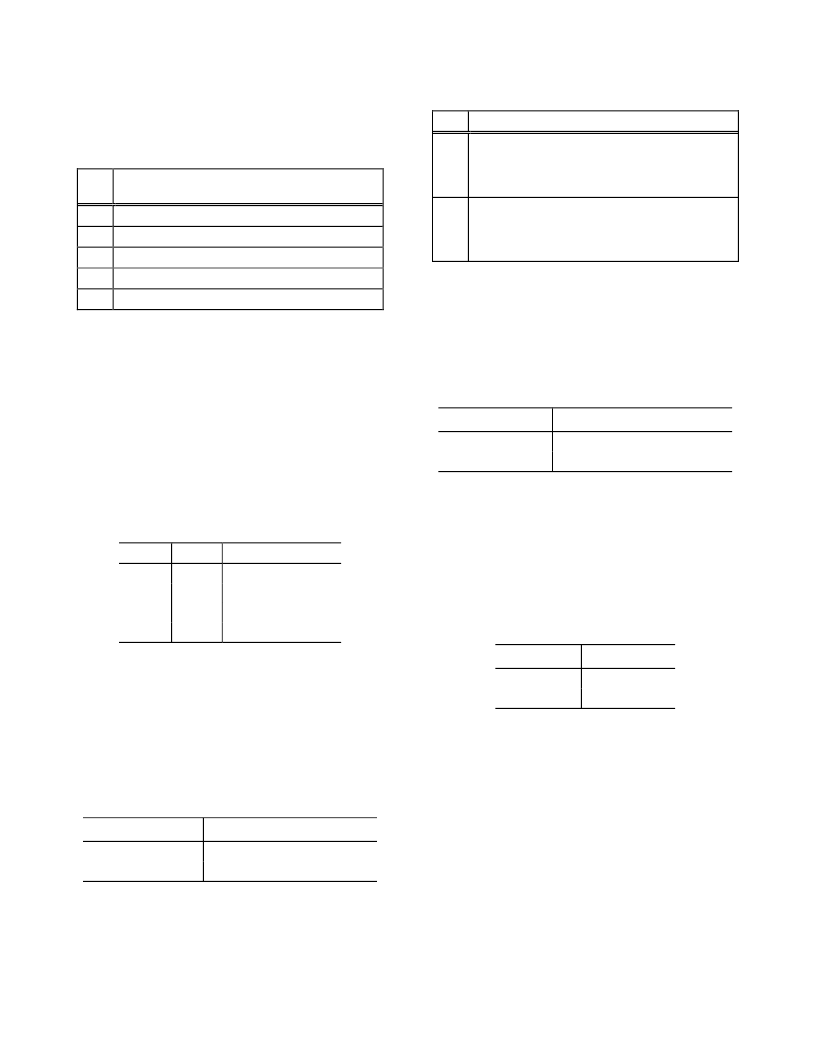

The two dynamic synthesizers are programmable as follows,

while each synthesizer may be independently disabled,

through the two

Disable Synthesizer

flags in the

SYNTHESIZER PROGRAM CC Control Register 72.

Bit

SYNTHESIZER PROGRAM CC Control Register

72

5

Disable Synthesizer 1

4

Disable Synthesizer 0

3

Synthesizer Enable Select

2

Synthesizer Mode

1 : 0

Pin Mode (1:0)

SYNTHEN0 : 1

The AD6426 provides enable signals for two independent

synthesizers. These signals are available at the output pins

SYNTHEN0 and SYNTHEN1. The polarities of these signals

are individually programmable; i.e. bit 7 of CC Control

Register 38 is applied to the synthesizer selected by either bit

2 or bit 1 of the same register.

SYNTHDATA and SYNTHCLK

Three Modes can be selected to support different radio

architectures. The selection of the Pin-Mode is done by the

two

Pin Mode

flags in the SYNTHESIZER PROGRAM CC

Control Register 72 as shown in Table 14.

Table 14. Pin Mode

Bit 1

Bit 0

Mode

0

0

1

1

0

1

0

1

Mode 1 (default)

Mode 1

Mode 2

Mode 3

The default is Mode 1, which supports TTP/Hitachi Bright

and Philips radio architectures. Mode 2 also supports a Philips

architecture, while Mode 3 supports a Siemens architecture. In

Mode 1, the pins SYNTHDATA and SYNTHCLK have their

original functionality; i.e. SYNTHDATA is the data output

and SYNTHCLK is the clock output of the serial synthesizer

interface. Clock polarity and frequency are programmed in the

SYNTH CONTROL CC Control Register 38.

Table 15. Pin Function in Mode 1

AD6426 Pin

Function

SYNTHDATA

SYNTHCLK

Synthesizer Data

Synthesizer Clock

Bit

SYNTH CONTROL CC Control Register 38

5

Synthesizer Clock Polarity

Selects the edge, on which synthesizer data and

enable will be clocked out. Negative edge, when set

to 0; positive edge, when set to 1.

0

Synthesizer Clock

;

selects the frequency of SYNTHCLK output.

SYNTHCLK = 1.625 MHz if set to 0 (default),

SYNTHCLK = 6.5 MHz if set to 1.

In Modes 2 and 3, the outputs of these two pins are

multiplexed with flags of the internal DSP as indicated in

Table 16. The function of DSPFLAG1

Synthesizer Data is

defined as: The output is that of DSPFLAG1 except when the

synthesizer interface is active. In this case the synthesizer

output has priority. The same applies to DSPFLAG2

Synthesizer Clock.

Table 16. Pin Function in Modes 2 and 3

AD6426 Pin

Function

SYNTHDATA

SYNTHCLK

DSPFLAG1

Synthesizer Data

DSPFLAG2

Synthesizer Clock

AGC Control

AGC programming is achieved in one of three ways:

The first is a gain select approach, whereby the DSPFLAG0

and DSPFLAG1 are used as a 2-bit gain selector (AGCA,

AGCB). This is available in Mode 1 and the flags are under

direct control of the internal DSP and are timing independent

of the synthesizer interface.

Table 17. Pin Function in Mode 1

AD6426 Pin

Function

AGCA

AGCB

DSPFLAG0

DSPFLAG1

The second is through the DSP combined with the serial

synthesizer interface, as defined in Mode 2. The function of

DSPFLAG0

SYNTHEN1 is defined as: The output is that of

DSPFLAG0 except when the synthesizer interface is active.

To support the Philips chipset whereby the AGC and the PLL

are programmed over the same enable line, the AGCA pin is

multiplexed to provide a SYNTHEN1 gated with DSPFLAG0.

This pin would be wired instead of the SYNTHEN1 pin. Since

the DSP would program the AGC during RXON, and the

synthesizers are reprogrammed following the end of the active

phase, no conflict can occur.

相關PDF資料 |

PDF描述 |

|---|---|

| AD642J | Precision, Low Cost Dual BiFET Op Amp |

| AD642K | SCHOTTKY DIODE DO-204AL 40V 1A |

| AD642L | Precision, Low Cost Dual BiFET Op Amp |

| AD642S | Precision, Low Cost Dual BiFET Op Amp |

| AD642 | Precision, Low Cost Dual BiFET Op Amp |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD642J | 制造商:AD 制造商全稱:Analog Devices 功能描述:Precision, Low Cost Dual BiFET Op Amp |

| AD642JH | 制造商:Rochester Electronics LLC 功能描述:PRECISION DUAL OP AMP IC - Bulk |

| AD642K | 制造商:AD 制造商全稱:Analog Devices 功能描述:Precision, Low Cost Dual BiFET Op Amp |

| AD642KH | 制造商:Rochester Electronics LLC 功能描述:PRECISION DUAL OP AMP IC - Bulk 制造商:Analog Devices 功能描述: |

| AD642L | 制造商:AD 制造商全稱:Analog Devices 功能描述:Precision, Low Cost Dual BiFET Op Amp |

發(fā)布緊急采購,3分鐘左右您將得到回復。