- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373901 > AD7476BRTZ-REEL7 (ANALOG DEVICES INC) 1 MSPS, 12-/10-/8-Bit ADCs in 6-Lead SOT-23 PDF資料下載

參數(shù)資料

| 型號(hào): | AD7476BRTZ-REEL7 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類(lèi): | ADC |

| 英文描述: | 1 MSPS, 12-/10-/8-Bit ADCs in 6-Lead SOT-23 |

| 中文描述: | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO6 |

| 封裝: | PLASTIC, LEAD FREE, MO-178AB, SOT-23, 6 PIN |

| 文件頁(yè)數(shù): | 2/20頁(yè) |

| 文件大小: | 360K |

| 代理商: | AD7476BRTZ-REEL7 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

REV. D

–2–

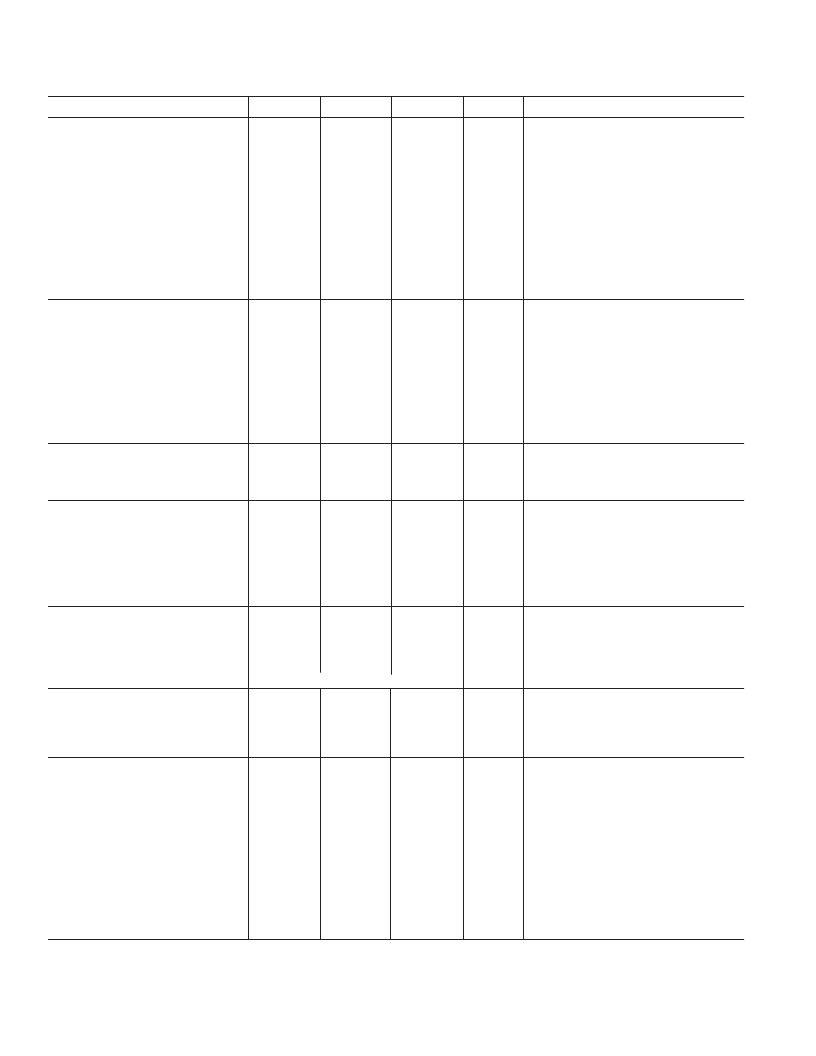

AD7476–SPECIFICATIONS

1

(A Version: V

DD

= 2.7 V to 5.25 V, f

SCLK

= 20 MHz, f

SAMPLE

= 1 MSPS, unless otherwise

noted; S and B Versions: V

DD

= 2.35 V to 5.25 V, f

SCLK

= 12 MHz, f

SAMPLE

= 600 kSPS,

unless otherwise noted; T

A

= T

MIN

to T

MAX

, unless otherwise noted.)

Parameter

A Version

1, 2

B Version

1, 2

S Version

1, 2

Unit

Test Conditions/Comments

DYNAMIC PERFORMANCE

Signal-to-(Noise + Distortion) (SINAD)

3

f

= 100 kHz Sine Wave

B Version, V

DD

= 2.4 V to 5.25 V

T

A

= 25

°

C

69

70

70

69

70

dB min

dB min

dB typ

dB min

dB typ

dB typ

dB typ

71.5

71

72.5

–78

–80

Signal-to-Noise Ratio (SNR)

3

70

70

B Version, V

DD

= 2.4 V to 5.25 V

Total Harmonic Distortion (THD)

3

Peak Harmonic or Spurious Noise (SFDR)

3

Intermodulation Distortion (IMD)

Second-Order Terms

Third-Order Terms

Aperture Delay

Aperture Jitter

Full Power Bandwidth

–80

–82

–78

–80

–78

–78

10

30

6.5

–78

–78

10

30

6.5

–78

–78

10

30

6.5

dB typ

dB typ

ns typ

ps typ

MHz typ

fa = 103.5 kHz, fb = 113.5 kHz

fa = 103.5 kHz, fb = 113.5 kHz

@ 3 dB

DC ACCURACY

S, B Versions, V

DD

= (2.35 V to 3.6 V)

4

;

A Version, V

DD

= (2.7 V to 3.6 V)

Resolution

Integral Nonlinearity

3

12

12

±

1.5

±

0.6

–0.9/+1.5

±

0.75

±

1.5

12

±

1.5

±

0.6

–0.9/+1.5

±

0.75

±

2

Bits

LSB max

LSB typ

LSB max

LSB typ

LSB max

LSB typ

LSB max

LSB typ

±

1

Differential Nonlinearity

3

Guaranteed No Missed Codes to 12 Bits

±

0.75

Offset Error

3

±

0.5

Gain Error

3

±

1.5

±

2

±

0.5

ANALOG INPUT

Input Voltage Ranges

DC Leakage Current

Input Capacitance

0 to V

DD

±

1

30

0 to V

DD

±

1

30

0 to V

DD

±

1

30

V

μ

A max

pF typ

LOGIC INPUTS

Input High Voltage, V

INH

2.4

1.8

0.4

0.8

±

1

±

1

10

2.4

1.8

0.4

0.8

±

1

±

1

10

2.4

1.8

0.4

0.8

±

1

±

1

10

V min

V min

V max

V max

μ

A max

μ

A typ

pF max

V

DD

= 2.35 V

V

DD

= 3 V

V

DD

= 5 V

Typically 10 nA, V

IN

= 0 V or V

DD

Input Low Voltage, V

INL

Input Current, I

IN

, SCLK Pin

Input Current, I

IN

,

CS

Pin

Input Capacitance, C

IN5

LOGIC OUTPUTS

Output High Voltage, V

OH

Output Low Voltage, V

OL

Floating-State Leakage Current

Floating-State Output Capacitance

Output Coding

V

DD

– 0.2

0.4

±

10

10

Straight (Natural) Binary

V

DD

– 0.2

0.4

±

10

10

V

DD

– 0.2

0.4

±

10

10

V min

V max

μ

A max

pF max

I

SOURCE

= 200

μ

A; V

DD

= 2.35 V to 5.25 V

I

SINK

μ

A

CONVERSION RATE

Conversion Time

Track-and-Hold Acquisition Time

0.8

500

350

1000

1.33

500

400

600

1.33

500

400

600

μ

s max

ns max

ns max

kSPS max

16 SCLK Cycles

Full-Scale Step Input

Sine Wave Input

≤

100 kHz

See Serial Interface Section

Throughput Rate

POWER REQUIREMENTS

V

DD

I

DD

Normal Mode (Static)

2.35/5.25

2.35/5.25

2.35/5.25

V min/max

Digital I/Ps = 0 V or V

V

DD

= 4.75 V to 5.25 V. SCLK On or Off

V

DD

= 2.35 V to 3.6 V. SCLK On or Off

V

DD

= 4.75 V to 5.25 V; f

SAMPLE

= f

SAMPLE

MAX

6

V

DD

= 2.35 V to 3.6 V; f

SAMPLE

= f

SAMPLE

MAX

6

SCLK Off

SCLK On

2

1

3.5

1.6

1

80

2

1

3

1.4

1

80

2

1

3

1.4

1

80

mA typ

mA typ

mA max

mA max

μ

A max

μ

A max

Normal Mode (Operational)

Full Power-Down Mode

Power Dissipation

7

Normal Mode (Operational)

17.5

4.8

5

3

15

4.2

5

3

15

4.2

5

3

mW max

mW max

μ

W max

μ

W max

V

DD

= 5 V; f

SAMPLE

= f

SAMPLE

MAX

6

V

DD

= 3 V; f

= f

SAMPLE

MAX

6

V

DD

= 5 V; SCLK Off

V

DD

= 3 V; SCLK Off

Full Power-Down

NOTES

1

Temperature ranges as follows: A, B Versions: –40

°

C to +85

°

C; S Version: –55

°

C to +125

°

C.

2

Operational from V

= 2.0 V.

3

See Terminology section.

4

Maximum B, S version specifications apply as typical figures when V

DD

= 5.25 V.

5

Guaranteed by characterization.

6

A Version: f

MAX = 1 MSPS; B, S Versions: f

SAMPLE

MAX = 600 kSPS.

7

See Power vs. Throughput Rate section.

Specifications subject to change without notice.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7476SRTZ-REEL7 | 1 MSPS, 12-/10-/8-Bit ADCs in 6-Lead SOT-23 |

| AD7477 | 1MSPS,10 Bit ADCs in 6 Lead SOT-23(10位高速,低耗,逐次逼近式A/D轉(zhuǎn)換器) |

| AD7476 | 1MSPS,12-Bit ADCs in 6 Lead SOT-23(12位高速,低耗,逐次逼近式A/D轉(zhuǎn)換器) |

| AD7482 | 3MSPS, 12-Bit SAR ADC |

| AD7482AST | 3MSPS, 12-Bit SAR ADC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7476BRTZ-REEL73 | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 MSPS, 12-/10-/8-Bit ADCs in 6-Lead SOT-23 |

| AD7476SRT | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 MSPS, 12-/10-/8-Bit ADCs in 6-Lead SOT-23 |

| AD7476SRT-500RL7 | 制造商:Analog Devices 功能描述:ADC Single SAR 600ksps 12-bit Serial 6-Pin SOT-23 T/R 制造商:Rochester Electronics LLC 功能描述:12-BIT ADC IN SOT I.C. - Bulk |

| AD7476SRT-R2 | 制造商:Analog Devices 功能描述:ADC Single SAR 600ksps 12-bit Serial 6-Pin SOT-23 T/R |

| AD7476SRT-REEL | 制造商:AD 制造商全稱:Analog Devices 功能描述:1 MSPS, 12-/10-/8-Bit ADCs in 6-Lead SOT-23 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。