- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄17059 > AD9114-DPG2-EBZ (Analog Devices Inc)IC DAC DUAL 8BIT LO PWR 40LFCSP PDF資料下載

參數(shù)資料

| 型號: | AD9114-DPG2-EBZ |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 32/52頁 |

| 文件大小: | 0K |

| 描述: | IC DAC DUAL 8BIT LO PWR 40LFCSP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | TxDAC® |

| DAC 的數(shù)量: | 2 |

| 位數(shù): | 8 |

| 采樣率(每秒): | 125M |

| 數(shù)據(jù)接口: | 串行 |

| DAC 型: | 電流 |

| 工作溫度: | -40°C ~ 85°C |

| 已供物品: | 板 |

| 已用 IC / 零件: | AD9114 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

AD9114/AD9115/AD9116/AD9117

Data Sheet

Rev. C | Page 38 of 52

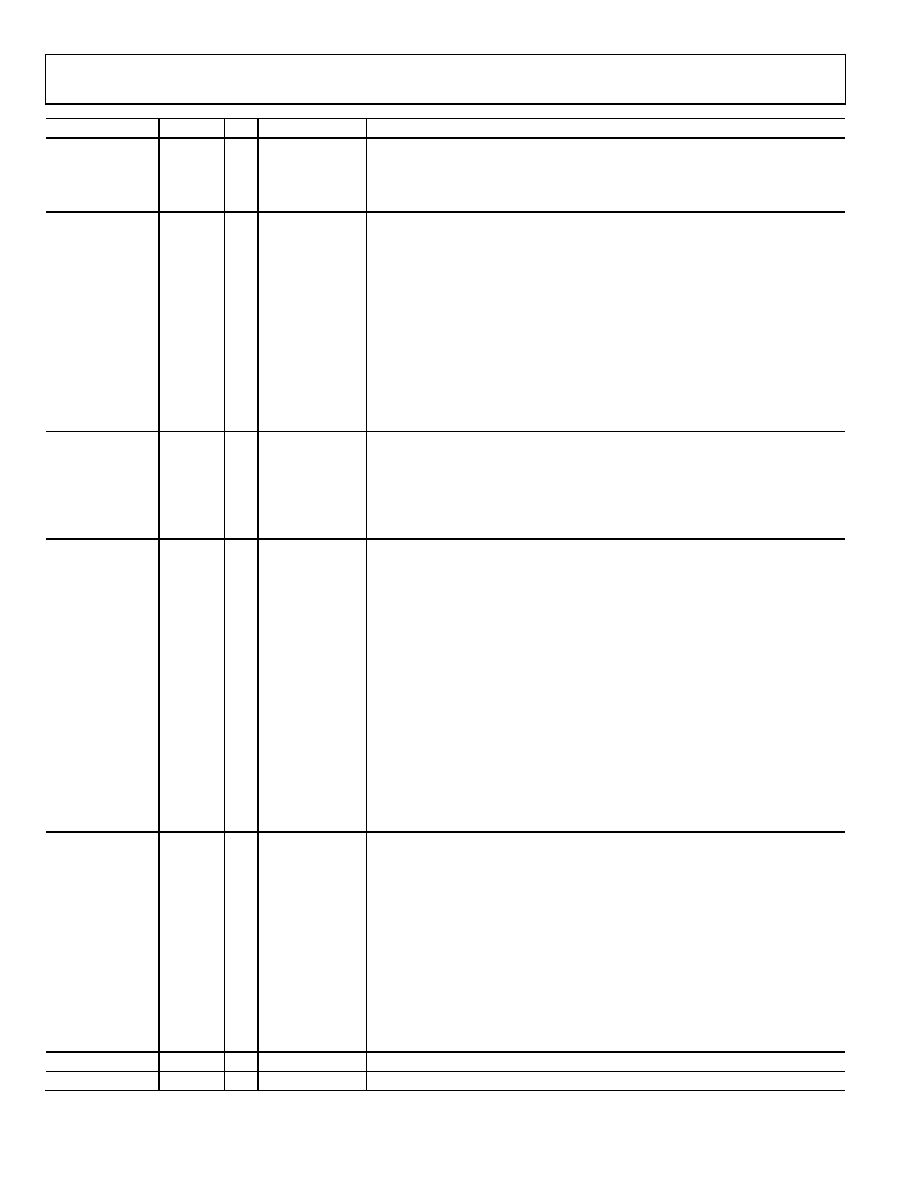

Register

Address

Bit

Name

Description

AUXDAC I

0x0B

7:0

IAUXDAC[7:0]

AUXDAC I output voltage adjustment word LSBs.

0x3FF: sets AUXDAC I output to full scale.

0x200: sets AUXDAC I output to midscale.

0x000 (default): sets AUXDAC I output to bottom of scale.

AUX CTLI

0x0C

7

IAUXEN

0 (default): AUXDAC I output disabled.

1: enables AUXDAC I output.

6:5

IAUXRNG[1:0]

00 (default): sets AUXDAC I output voltage range to 2 V.

01: sets AUXDAC I output voltage range to 1.5 V.

10: sets AUXDAC I output voltage range to 1.0 V.

11: sets AUXDAC I output voltage range to 0.5 V.

4:2

IAUXOFS[2:0]

000 (default): sets AUXDAC I top of range to 1.0 V.

001: sets AUXDAC I top of range to 1.5 V.

010: sets AUXDAC I top of range to 2.0 V.

011: sets AUXDAC I top of range to 2.5 V.

100: sets AUXDAC I top of range to 2.9 V.

1:0

IAUXDAC[9:8]

AUX DAC I output voltage adjustment word MSBs (default = 00).

Reference

Resistor

0x0D

5:0

RREF[5:0]

Permits an adjustment of the on-chip reference voltage and output at REFIO (see

Figure 97) twos complement.

000000 (default): sets the value of RREF to 10 k, VREF = 1.0 V.

011111: sets the value of RREF to 12 k, VREF = 1.2 V.

100000: sets the value of RREF to 8 k, VREF = 0.8 V.

111111: sets the value of RREF to 10 k, VREF = 1.0 V.

Cal Control

0x0E

7

PRELDQ

0 (default): preloads Q DAC calibration reference set to 32.

1: preloads Q DAC calibration reference set by user (Cal Address 1).

6

PRELDI

0 (default): preloads I DAC calibration reference set to 32.

1: preloads I DAC calibration reference set by user (Cal Address 1).

5

CALSELQ

0 (default): Q DAC self-calibration done.

1: selects Q DAC self-calibration.

4

CALSELI

0 (default): I DAC self-calibration done.

1: selects I DAC self-calibration.

3

CALCLK

0 (default): calibration clock disabled.

1: calibrates clock enabled.

2:0

DIVSEL[2:0]

Calibration clock divide ratio from DAC clock rate.

000 (default): divide by 256.

001: divide by 128.

…

110: divide by 4.

111: divide by 2.

Cal Memory

0x0F

7

CALSTATQ

0 (default): Q DAC calibration in progress.

1: calibration of Q DAC complete.

6

CALSTATI

0 (default): I DAC calibration in progress.

1: calibration of I DAC complete.

3:2

CALMEMQ[1:0]

Status of Q DAC calibration memory.

00 (default): uncalibrated.

01: self-calibrated.

10: user-calibrated.

1:0

CALMEMI[1:0]

Status of I DAC calibration memory.

00 (default): uncalibrated.

01: self-calibrated.

10: user-calibrated.

Memory Address

0x10

5:0

MEMADDR[5:0]

Address of static memory to be accessed.

Memory Data

0x11

5:0

MEMDATA[5:0]

Data for static memory access.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9115-DPG2-EBZ | IC DAC DUAL 10BIT LO PWR 40LFCSP |

| 0210490184 | CABLE JUMPER 1.25MM .229M 12POS |

| RCM15DCCN-S189 | CONN EDGECARD 30POS R/A .156 SLD |

| CDB4382A | BOARD EVAL FOR CS4382A DAC |

| 0210490183 | CABLE JUMPER 1.25MM .229M 12POS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9114-EBZ | 制造商:Analog Devices 功能描述:DUAL 8 BIT LOW POWER CONVERTER - Boxed Product (Development Kits) |

| AD9115 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Dual, 8-/10-/12-/14-Bit Low Power Digital-to-Analog Converters |

| AD91151Z | 制造商:Analog Devices 功能描述: |

| AD91154Z | 制造商:Analog Devices 功能描述:SCREENED DSP PART - Rail/Tube |

| AD91156-05 | 制造商:Analog Devices 功能描述:IC,ADSP-BF561SKB600,16BIT,600MHZ,DUAL CO |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。