- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373961 > AD9238BST-65 (ANALOG DEVICES INC) 12-Bit, 20/40/65 MSPS Dual A/D Converter PDF資料下載

參數(shù)資料

| 型號: | AD9238BST-65 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 12-Bit, 20/40/65 MSPS Dual A/D Converter |

| 中文描述: | 2-CH 12-BIT FLASH METHOD ADC, PARALLEL ACCESS, PQFP64 |

| 封裝: | LEAD FREE, MS-026-BBD, LQFP-64 |

| 文件頁數(shù): | 3/24頁 |

| 文件大?。?/td> | 1737K |

| 代理商: | AD9238BST-65 |

AD9238

–3–

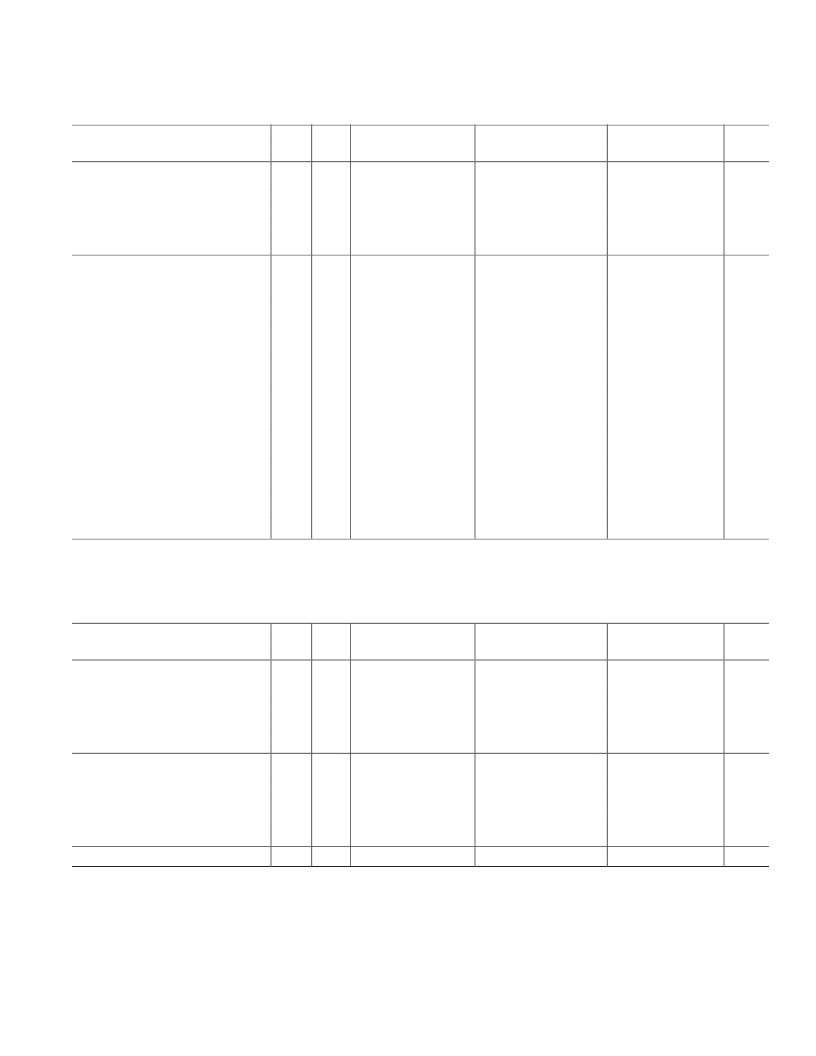

DC SPECIFICATIONS

Test

AD9238BST-20

Typ

AD9238BST-40

Min

Typ

AD9238BST-65

Min

Typ

Parameter

LOGIC INPUTS

High Level Input Voltage

Low Level Input Voltage

High Level Input Current

Low Level Input Current

Input Capacitance

LOGIC OUTPUTS

*

DRVDD = 3.3 V

High Level Output Voltage

(IOH = 50 mA)

High Level Output Voltage

(IOH = 0.5 mA)

Low Level Output Voltage

(IOL = 50 mA)

Low Level Output Voltage

(IOL = 1.6 mA)

DRVDD = 2.5 V

High Level Output Voltage

(IOH = 50 mA)

High Level Output Voltage

(IOH = 0.5 mA)

Low Level Output Voltage

(IOL = 50 mA)

Low Level Output Voltage

(IOL = 1.6 mA)

Temp Level Min

Max

Max

Max

Unit

Full

Full

Full

Full

Full

IV

IV

IV

IV

V

2.0

2.0

2.0

V

V

μA

μA

pF

0.8

+10

+10

0.8

+10

+10

0.8

+10

+10

–10

–10

–10

–10

–10

–10

2

2

2

Full

IV

3.29

3.29

3.29

V

Full

IV

3.25

3.25

3.25

V

Full

IV

0.05

0.05

0.05

V

Full

IV

0.2

0.2

0.2

V

Full

IV

2.49

2.49

2.49

V

Full

IV

2.45

2.45

2.45

V

Full

IV

0.05

0.05

0.05

V

Full

IV

0.2

0.2

0.2

V

*

Output Voltage Levels measured with 5 pF load on each output.

Specifications subject to change without notice.

SWITCHING SPECIFICATIONS

Test

AD9238BST-20

Typ

AD9238BST-40

Min

Typ

AD9238BST-65

Min

Typ

Parameter

SWITCHING PERFORMANCE

Max Conversion Rate

Min Conversion Rate

CLK Period

CLK Pulsewidth High

1

CLK Pulsewidth Low

1

DATA OUTPUT PARAMETERS

Output Delay

2

(t

PD

)

Pipeline Delay (Latency)

Aperture Delay (t

A

)

Aperture Uncertainty (t

J

)

Wake-Up Time

3

OUT-OF-RANGE RECOVERY TIME Full

Temp Level Min

Max

Max

Max

Unit

Full

Full

Full

Full

Full

VI

V

V

V

V

20

40

65

MSPS

MSPS

ns

ns

ns

1

1

1

50.0

15.0

15.0

25.0

8.8

8.8

15.4

6.2

6.2

Full

Full

Full

Full

Full

IV

V

V

V

V

V

2

3.5

7

1.0

0.5

2.5

1

6

2

3.5

7

1.0

0.5

2.5

1

6

2

3.5

7

1.0

0.5

2.5

2

6

ns

Cycles

ns

ps rms

ms

Cycles

NOTES

1

The AD9238-65 model has a duty cycle stabilizer circuit that, when enabled, corrects for a wide range of duty cycles (see TPC 20).

2

Output delay is measured from CLOCK 50% transition to DATA 50% transition, with a 5 pF load on each output.

3

Wake-up time is dependent on the value of the decoupling capacitors; typical values shown with 0.1 μF and 10 μF capacitors on REFT and REFB.

Specifications subject to change without notice.

(continued)

REV. A

相關PDF資料 |

PDF描述 |

|---|---|

| AD9238BSTRL-20 | 12-Bit, 20/40/65 MSPS Dual A/D Converter |

| AD9238BSTRL-40 | 12-Bit, 20/40/65 MSPS Dual A/D Converter |

| AD9238BSTRL-65 | 12-Bit, 20/40/65 MSPS Dual A/D Converter |

| AD9240 | Complete 14-Bit, 10 MSPS Monolithic A/D Converter |

| AD9240AS | Complete 14-Bit, 10 MSPS Monolithic A/D Converter |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AD9238BST-65PCB | 制造商:Analog Devices 功能描述:Evaluation Board For AD9238 Dual A/D Converter ,12-Bit, 20 MSPS/40 MSPS/65 MSPS 制造商:Rochester Electronics LLC 功能描述:DUAL 12 BIT 3V CMOS 20/40/65 MSPS ADC - Bulk |

| AD9238BST-65PCBZ | 制造商:Analog Devices 功能描述:DUAL 12 BIT 3V CMOS 20/40/65 MSPS ADC - Bulk |

| AD9238BSTRL-20 | 制造商:Rochester Electronics LLC 功能描述:DUAL 12 BIT 3V CMOS 20/40/65 MSPS ADC - Bulk 制造商:Analog Devices 功能描述: |

| AD9238BSTRL-40 | 功能描述:IC ADC 12BIT DUAL 40MSPS 64-LQFP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數(shù):12 采樣率(每秒):3M 數(shù)據(jù)接口:- 轉(zhuǎn)換器數(shù)目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數(shù)目和類型:- |

| AD9238BSTRL-65 | 功能描述:IC ADC 12BIT DUAL 65MSPS 64-LQFP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數(shù):12 采樣率(每秒):3M 數(shù)據(jù)接口:- 轉(zhuǎn)換器數(shù)目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數(shù)目和類型:- |

發(fā)布緊急采購,3分鐘左右您將得到回復。