- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384089 > ADC1206S070H (NXP Semiconductors N.V.) Single 12 bits ADC up to 70 Msps PDF資料下載

參數(shù)資料

| 型號: | ADC1206S070H |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 外設(shè)及接口 |

| 英文描述: | Single 12 bits ADC up to 70 Msps |

| 封裝: | ADC1206S070H/C1<SOT307-2 (QFP44)|<<http://www.nxp.com/packages/SOT307-2.html<1<Always Pb-free,;ADC1206S070H/C1<SOT307-2 (QFP44)|<<http://www.nxp.com/packages/SOT307-2.htm |

| 文件頁數(shù): | 12/32頁 |

| 文件大小: | 513K |

| 代理商: | ADC1206S070H |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

ADC1206S040_055_070_2

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 02 — 12 August 2008

12 of 32

NXP Semiconductors

ADC1206S040/055/070

Single 12 bits ADC, up to 40 MHz, 55 MHz or 70 MHz

[1]

D = guaranteed by design; C = guaranteed by characterization; I = 100 % industrially tested.

[2]

The circuit has two clock inputs: CLK and CLKN. There are 5 modes of operation:

a) PECL mode 1: (DC level vary 1:1 with V

CCD

) CLK and CLKN inputs are at differential PECL levels.

b) PECL mode 2: (DC level vary 1:1 with V

CCD

) CLK input is at PECL level and sampling is taken on the falling edge of the clock input

signal. A DC level of 3.65 V has to be applied on CLKN decoupled to GND via a 100 nF capacitor.

c) PECL mode 3: (DC level vary 1:1 with V

CCD

) CLKN input is at PECL level and sampling is taken on the rising edge of the clock input

signal. A DC level of 3.65 V has to be applied on CLK decoupled to GND via a 100 nF capacitor.

d) Differential AC driving mode 4: When driving the CLK input directly and with any AC signal of minimum 1 V (p - p) and with a DC

level of 2.5 V, the sampling takes place at the falling edge of the clock signal. When driving the CLKN input with the same signal,

sampling takes place at the rising edge of the clock signal. It is recommended to decouple the CLKN or CLK input to DGND via a

100 nF capacitor.

e) TTL mode 1: CLK input is at TTL level and sampling is taken on the falling edge of the clock input signal.

In that case the CLKN pin has to be connected to the ground.

[3]

The ADC input range can be adjusted with an external reference connected to V

ref

pin. This voltage has to be referenced to V

CCA

;

see

Figure 12

.

[4]

The

3 dB analog bandwidth is determined by the 3 dB reduction in the reconstructed output, the input being a full-scale sine wave.

[5]

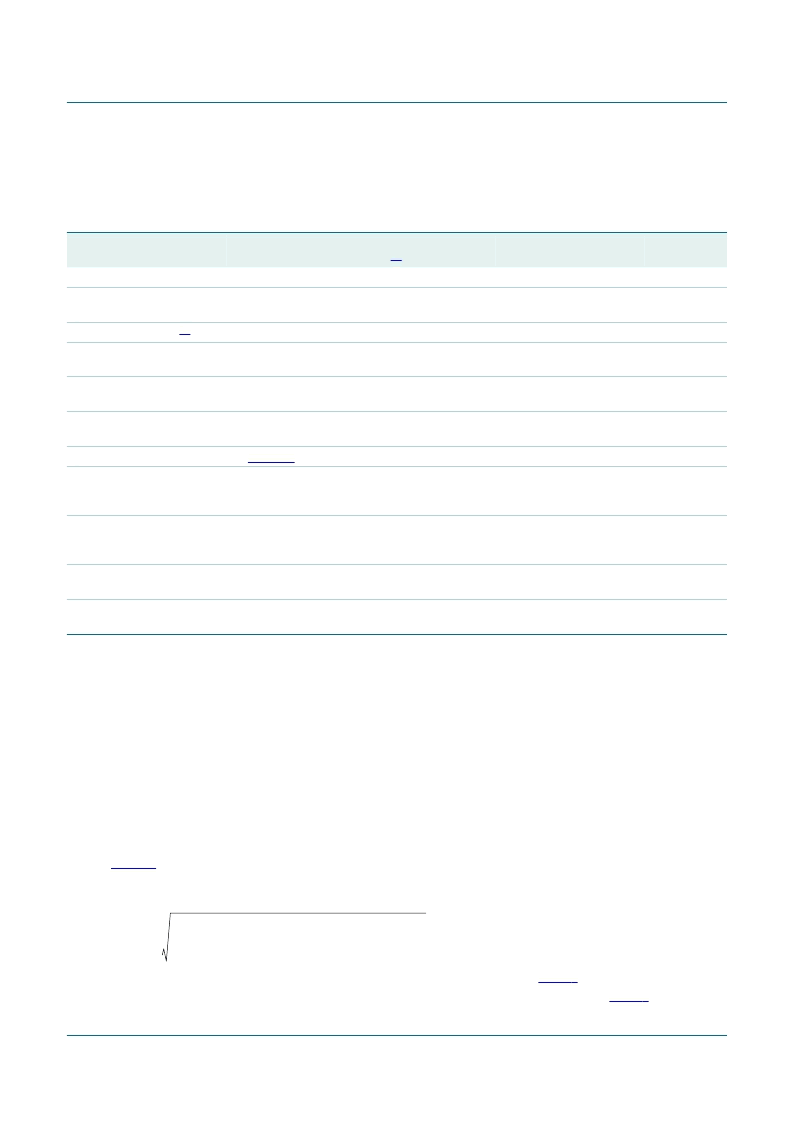

Total Harmonic Distortion (THD) is obtained with the addition of the first five harmonics:

where

α

1H

is the fundamental harmonic referenced at 0 dB for a full-scale sine wave input; see

Figure 6

.

Signal-to-noise ratio (S/N) takes into account all harmonics above five and noise up to Nyquist frequency; see

Figure 8

.

[6]

Bit error rate (f

clk

= 55 MHz)

BER

bit error rate

f

i

= 20 MHz; V

I

=

±

16 LSB at

code 2047

C

-

10

14

-

times/sample

Timing (C

L

= 10 pF)

[9]

t

d(s)

sampling delay

time

output hold

time

output delay

time

C

-

0.25

1

ns

t

h(o)

C

4

6.4

-

ns

t

d(o)

C

-

9.0

13

ns

3-state output delay times; see

Figure 4

t

dZH

float to active

HIGH delay

time

t

dZL

float to active

LOW delay

time

t

dHZ

active HIGH to

float delay time

t

dLZ

active LOW to

float delay time

C

-

5.1

9.0

ns

C

-

7.0

11

ns

C

-

9.7

14

ns

C

-

9.5

13

ns

Table 6.

V

CCA

= V2 to V44, V3 to V4 and V41 to V40 = 4.75 V to 5.25 V; V

CCD

= V37 to V38 and V15 to V17 = 4.75 V to 5.25 V;

V

CCO

= V33 to V34 = 3.0 V to 3.6 V; AGND and DGND shorted together; T

amb

=

40

°

C to 85

°

C;

V

I(IN)(p-p)

V

I(INN)(p-p)

= 1.9 V; V

ref

= V

CCA3

1.75 V; V

I(cm)

= V

CCA3

1.6 V; typical values measured at V

CCA

= V

CCD

= 5 V

and V

CCO

= 3.3 V T

amb

= 25

°

C and C

L

= 10 pF; unless otherwise specified.

Symbol

Parameter

Conditions

Characteristics

…continued

Test

[1]

Min

Typ

Max

Unit

THD

20 log

α

-----------------------------------------------------------------------------------------------------------------------------------------------

(

)

2

α

(

)

2

α

α

1H

2

)

2

2

+

+

+

+

(

=

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADC1206S040 | |

| ADC1207S080HW | Single 12 bits ADC, up to 80 MHz with direct-ultra high IF sampling |

| ADC1207S080HW | Single 12 bits ADC, up to 80 MHz with direct-ultra high IF sampling |

| ADC1207S080 | |

| ADC1210S065HN | Single 12-bit ADC 65 Msps CMOS or LVDS DDR digital outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADC1206S070H/C1,51 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC SGL 12BIT ADC 70MSPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADC1206S070H/C1,55 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC IC ADC 12BIT PAR 70MHZ RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADC1206S070H/C1-T | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC SGL 12BIT ADC 70MSPS RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| ADC1206S070H-C1 | 制造商:Integrated Device Technology Inc 功能描述:QFP44 - Bulk |

| ADC1206S070H-C18 | 制造商:Integrated Device Technology Inc 功能描述:QFP44 - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。