- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362131 > ADC674ASH Microprocessor-Compatible ANALOG-TO-DIGITAL CONVERTER PDF資料下載

參數(shù)資料

| 型號: | ADC674ASH |

| 英文描述: | Microprocessor-Compatible ANALOG-TO-DIGITAL CONVERTER |

| 中文描述: | 微處理器兼容模擬到數(shù)字轉(zhuǎn)換器 |

| 文件頁數(shù): | 5/6頁 |

| 文件大小: | 56K |

| 代理商: | ADC674ASH |

5

ADC674A

STAND-ALONE OPERATION

For stand-alone operation, control of the converter is accom-

plished by a single control line connected to R/C. In this

mode CS and A

O

are connected to digital common and CE

and 12/8 are connected to V

LOGIC

(+5V). The output data are

presented as 12-bit words. The stand-alone mode is used in

systems containing dedicated input ports which do not

require full bus interface capability.

Conversion is initiated by a high-to-low transition of R/C.

The three-state data output buffers are enabled when R/C is

high and STATUS is low. Thus, there are two possible

modes of operation; conversion can be initiated with either

positive or negative pulses. In either case, the R/C pulse

must remain low for a minimum of 50ns.

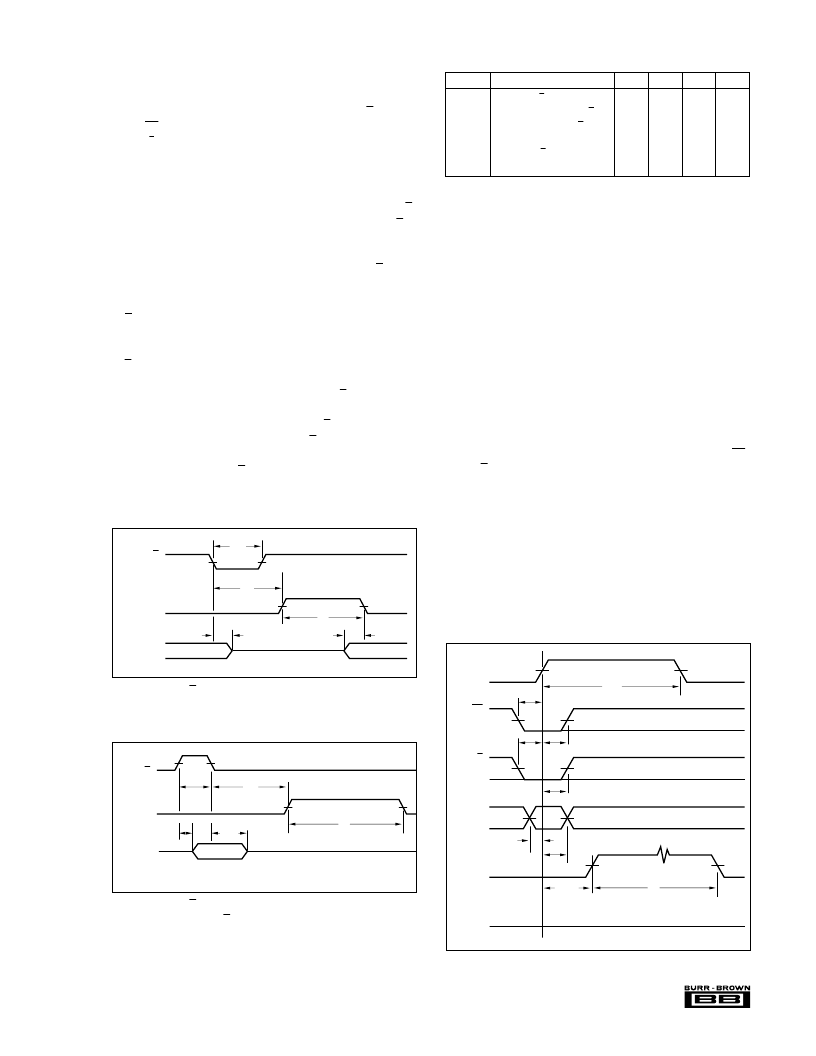

Figure 1 illustrates timing when conversion is initiated by an

R/C pulse which goes low and returns to the high state

during the conversion. In this case, the three-state outputs go

to the high-impedance state in response to the falling edge of

R/C and are enabled for external access of the data after

completion of the conversion. Figure 2 illustrates the timing

when conversion is initiated by a positive R/C pulse. In this

mode, the output data from the previous conversion is

enabled during the positive portion of R/C. A new conver-

sion is started on the falling edge of R/C, and the three-state

outputs return to the high impedance state until the next

occurrence of a high R/C pulse. Timing specifications for

stand-alone operation are listed in Table III.

FIGURE 2. R/C Pulse High—Outputs Enabled Only While

R/C is High.

FIGURE 1. R/C Pulse Low—Outputs Enabled After Con-

versions.

SYMBOL

PARAMETER

MIN

TYP

MAX

UNITS

t

HRL

t

DS

t

HDR

t

HS

t

HRH

t

DDR

Low R/C Pulse Width

STS Delay from R/C

Data Valid After R/C Low

STS Delay After Data Valid

High R/C Pulse Width

Data Access Time

50

ns

ns

ns

ns

ns

ns

200

25

300

150

400

1000

150

TABLE III. Stand-Alone Mode Timing.

FULLY CONTROLLED OPERATION

Conversion Length

Conversion length (8-bit or 12-bit) is determined by the state

of the A

O

input, which is latched upon receipt of a conver-

sion start transition (described below). If A

O

is latched high,

the conversion continues for 8 bits. The full 12-bit conver-

sion will occur if A

O

is low. If all 12 bits are read following

an 8-bit conversion the 3LSBs (DB0 - DB2) will be low

(logic 0) and DB3 will be high (logic 1). A

O

is latched because it is also involved in enabling the output

buffers. No other control inputs are latched.

CONVERSION START

The converter is commanded to initiate conversion by a

transition occurring on any of three logic inputs (CE, CS,

and R/C) as shown in Table II. Conversion is initiated by the

last of the three to reach the required state and thus all three

may be dynamically controlled. If necessary, all three may

change states simultaneously, and the nominal delay time is

the same regardless of which input actually starts conver-

sion. If it is desired that a particular input establish the actual

start of conversion, the other two should be stable a mini-

mum of 50ns prior to the transition of that input. Timing

relationships for start of conversion timing are illustrated in

Figure 3. The specifications for timing are contained in

Table IV.

FIGURE 3. Conversion Cycle Timing.

Data Valid

Data Valid

High-Z State

DB11-DB0

STATUS

R/C

t

HRL

t

DS

t

C

t

HS

t

HDR

Data Valid

High-Z State

DB11-DB0

STATUS

R/C

t

HRH

t

C

t

HDR

t

DDR

High-Z

t

DS

CE

t

SSC

t

HEC

CS

R/C

STATUS

t

C

DB11-DB0

A

O

t

SRC

t

HSC

t

HRC

t

SAC

t

HAC

t

DSC

High Impedance

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADC674ATH | Microprocessor-Compatible ANALOG-TO-DIGITAL CONVERTER |

| ADC674AJH | JT 9C 9#12 PIN PLUG |

| ADC700 | 16-Bit Resolution With Microprocessor Interface A/D CONVERTER |

| ADC700KH | 16-Bit Resolution With Microprocessor Interface A/D CONVERTER |

| ADC700RH | 16-Bit Resolution With Microprocessor Interface A/D CONVERTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADC674AT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Converter IC |

| ADC674AT/B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Converter IC |

| ADC674ATH | 制造商:BB 制造商全稱:BB 功能描述:Microprocessor-Compatible ANALOG-TO-DIGITAL CONVERTER |

| ADC674AU | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Converter IC |

| ADC674AU/B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Converter IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。