- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄294981 > AGL10005-FG256I FPGA, 1000000 GATES, 250 MHz, PBGA144 PDF資料下載

參數(shù)資料

| 型號(hào): | AGL10005-FG256I |

| 元件分類(lèi): | FPGA |

| 英文描述: | FPGA, 1000000 GATES, 250 MHz, PBGA144 |

| 封裝: | 13 X 13 MM, 1 MM PITCH, FBGA-144 |

| 文件頁(yè)數(shù): | 13/204頁(yè) |

| 文件大小: | 2800K |

| 代理商: | AGL10005-FG256I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)

IGLOO Low-Power Flash FPGAs with Flash*Freeze Technology

A d v an c ed v0 . 1

1-5

VersaTiles

The IGLOO core consists of VersaTiles, which have been enhanced beyond the ProASICPLUS core tiles. The IGLOO

VersaTile supports the following:

All 3-input logic functions—LUT-3 equivalent

Latch with clear or set

D-flip-flop with clear or set

Enable D-flip-flop with clear or set

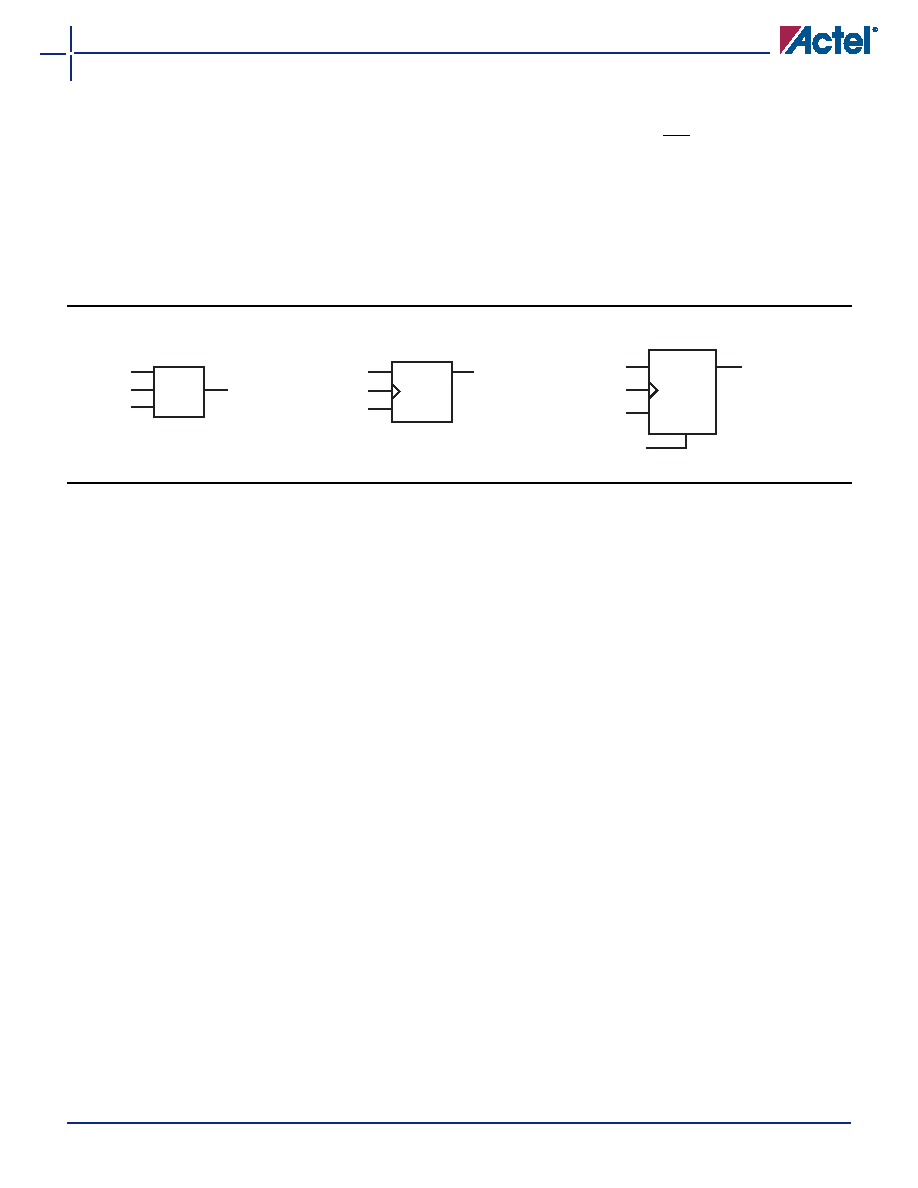

Refer to Figure 1-4 for VersaTile configurations.

For more information about VersaTiles, refer to the "VersaTile" section on page 2-2.

User Nonvolatile FlashROM

Actel IGLOO devices have 1 kbit of on-chip, user-

accessible, nonvolatile FlashROM. The FlashROM can be

used in diverse system applications:

Internet protocol addressing (wireless or fixed)

System calibration settings

Device serialization and/or inventory control

Subscription-based business models (for example,

set-top boxes)

Secure key storage for secure communications

algorithms

Asset management/tracking

Date stamping

Version management

The FlashROM is written using the standard IGLOO IEEE

1532 JTAG programming interface. The core can be

individually programmed (erased and written), and on-

chip AES decryption can be used selectively to securely

load data over public networks (except in the AGL030

device), as in security keys stored in the FlashROM for a

user design.

The FlashROM can be programmed via the JTAG

programming interface, and its contents can be read

back either through the JTAG programming interface or

via direct FPGA core addressing. Note that the FlashROM

can only be programmed from the JTAG interface and

cannot be programmed from the internal logic array.

The FlashROM is programmed as 8 banks of 128 bits;

however, reading is performed on a byte-by-byte basis

using a synchronous interface. A 7-bit address from the

FPGA core defines which of the 8 banks and which of the

16 bytes within that bank are being read. The three most

significant

bits

(MSBs)

of

the

FlashROM

address

determine the bank, and the four least significant bits

(LSBs) of the FlashROM address define the byte.

The Actel IGLOO development software solutions,

Libero

Integrated

Design

Environment

(IDE)

and

Designer, have extensive support for the FlashROM. One

such

feature

is

auto-generation

of

sequential

programming files for applications requiring a unique

serial number in each part. Another feature allows the

inclusion of static data for system version control. Data

for the FlashROM can be generated quickly and easily

using Actel Libero IDE and Designer software tools.

Comprehensive

programming

file

support

is

also

included to allow for easy programming of large

numbers of parts with differing FlashROM contents.

SRAM and FIFO

IGLOO

devices

(except

the

AGL030

device)

have

embedded SRAM blocks along their north and south

sides. Each variable-aspect-ratio SRAM block is 4,608 bits

in size. Available memory configurations are 256×18,

512×9, 1k×4, 2k×2, and 4k×1 bits. The individual blocks

have independent read and write ports that can be

configured with different bit widths on each port. For

example, data can be sent through a 4-bit port and read

as a single bitstream. The embedded SRAM blocks can be

initialized via the device JTAG port (ROM emulation

mode) using the UJTAG macro (except in the AGL030

device).

Figure 1-4 VersaTile Configurations

X1

Y

X2

X3

LUT-3

Data

Y

CLK

Enable

CLR

D-FF

Data

Y

CLK

CLR

D-FF

LUT-3 Equivalent

D-Flip-Flop with Clear or Set

Enable D-Flip-Flop with Clear or Set

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AGL10005-FG256 | FPGA, 1000000 GATES, 250 MHz, PBGA144 |

| AGL10005-FG484I | FPGA, 1000000 GATES, 250 MHz, PBGA484 |

| AGL10005-FG484 | FPGA, 1000000 GATES, 250 MHz, PBGA484 |

| AGL10005-FGG144I | FPGA, 1000000 GATES, 250 MHz, PBGA144 |

| AGL10005-FGG144 | FPGA, 1000000 GATES, 250 MHz, PBGA144 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AGL1000V2-CS144 | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:IGLOO Low-Power Flash FPGAs with Flash Freeze Technology |

| AGL1000V2-CS144ES | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:IGLOO Low-Power Flash FPGAs with Flash Freeze Technology |

| AGL1000V2-CS144I | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:IGLOO Low-Power Flash FPGAs with Flash Freeze Technology |

| AGL1000V2-CS144PP | 制造商:ACTEL 制造商全稱(chēng):Actel Corporation 功能描述:IGLOO Low-Power Flash FPGAs with Flash Freeze Technology |

| AGL1000V2-CS281 | 功能描述:IC FPGA 1KB FLASH 1M 281-CSP RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:IGLOO 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門(mén)數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。