- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄294984 > AGLP060V2-CSG289I FPGA, 1584 CLBS, 60000 GATES, PBGA289 PDF資料下載

參數(shù)資料

| 型號: | AGLP060V2-CSG289I |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 1584 CLBS, 60000 GATES, PBGA289 |

| 封裝: | 14 X 14 MM, 1.2 MM HEIGHT, 0.8 MM PITCH, ROHS COMPLIANT, CSP-289 |

| 文件頁數(shù): | 100/128頁 |

| 文件大小: | 4383K |

| 代理商: | AGLP060V2-CSG289I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁當(dāng)前第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁

IGLOO PLUS Low Power Flash FPGAs

Re vi s i on 11

2 - 59

1.2 V DC Core Voltage

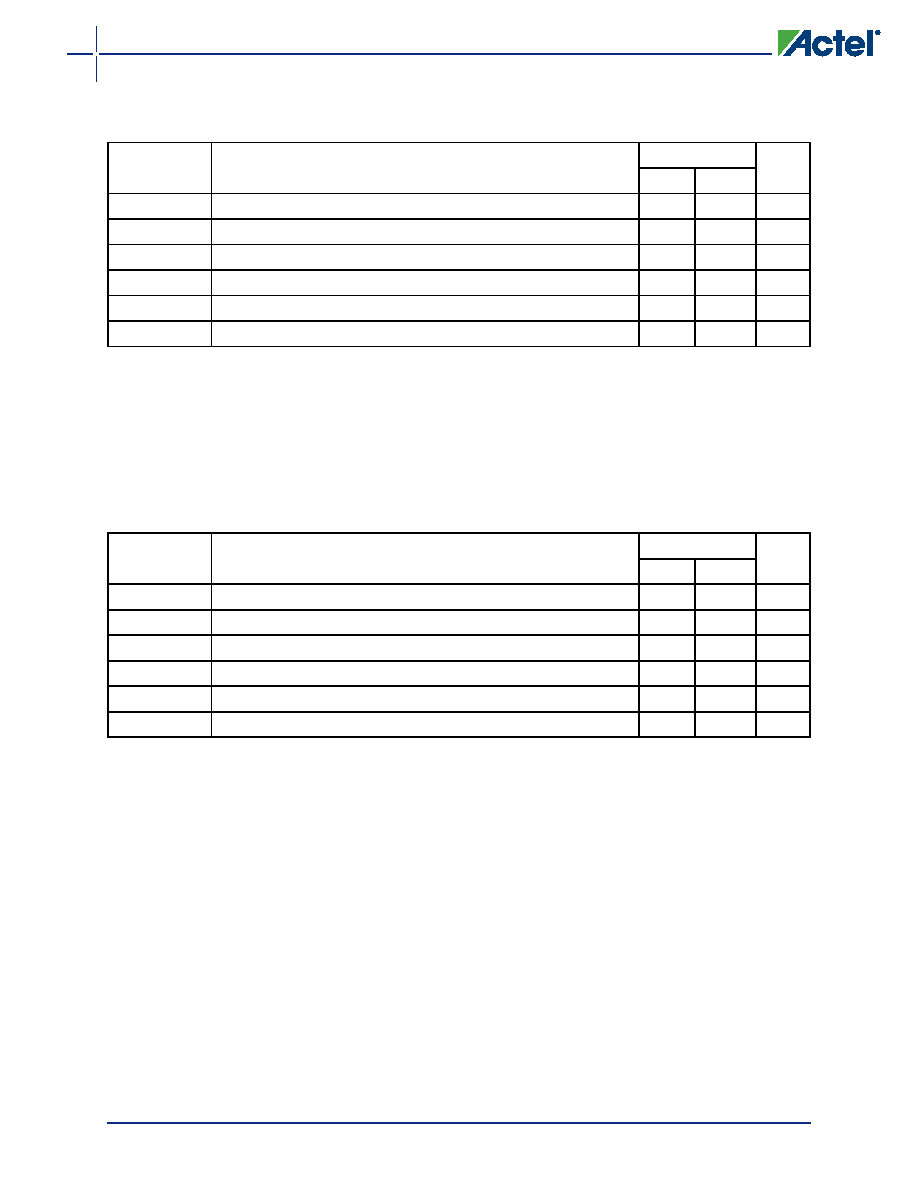

Table 2-86 AGLP125 Global Resource

Commercial-Case Conditions: TJ = 70°C, VCC = 1.425 V

Parameter

Description

Std.

Units

Min.1

Max.2

tRCKL

Input Low Delay for Global Clock

1.36

1.71

ns

tRCKH

Input High Delay for Global Clock

1.39

1.82

ns

tRCKMPWH

Minimum Pulse Width High for Global Clock

ns

tRCKMPWL

Minimum Pulse Width Low for Global Clock

ns

tRCKSW

Maximum Skew for Global Clock

0.43

ns

FRMAX

Maximum Frequency for Global Clock

MHz

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element,

located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully

loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-87 AGLP030 Global Resource

Commercial-Case Conditions: TJ = 70°C, VCC = 1.14 V

Parameter

Description

Std.

Units

Min.1

Max.2

tRCKL

Input Low Delay for Global Clock

1.80

2.09

ns

tRCKH

Input High Delay for Global Clock

1.88

2.27

ns

tRCKMPWH

Minimum Pulse Width High for Global Clock

ns

tRCKMPWL

Minimum Pulse Width Low for Global Clock

ns

tRCKSW

Maximum Skew for Global Clock

0.39

ns

FRMAX

Maximum Frequency for Global Clock

MHz

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element,

located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully

loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-7 for derating values.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AGLP060V2-CSG289 | FPGA, 1584 CLBS, 60000 GATES, PBGA289 |

| AGLP060V2-VQ176I | FPGA, 1584 CLBS, 60000 GATES, PQFP176 |

| AGLP060V2-VQ176 | FPGA, 1584 CLBS, 60000 GATES, PQFP176 |

| AGLP060V2-VQG176I | FPGA, 1584 CLBS, 60000 GATES, PQFP176 |

| AGLP060V2-VQG176 | FPGA, 1584 CLBS, 60000 GATES, PQFP176 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AGLP060-V2CSG289PP | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

| AGLP060-V2FCS289 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

| AGLP060-V2FCS289ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

| AGLP060-V2FCS289I | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

| AGLP060-V2FCS289PP | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:IGLOO PLUS Low-Power Flash FPGAs with FlashFreeze Technology |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。