- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄362193 > AK4120VF Converter PDF資料下載

參數(shù)資料

| 型號(hào): | AK4120VF |

| 英文描述: | Converter |

| 中文描述: | 轉(zhuǎn)換器 |

| 文件頁(yè)數(shù): | 7/30頁(yè) |

| 文件大小: | 247K |

| 代理商: | AK4120VF |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)

ASAHI KASEI

[AK4120]

MS0134-E-00

2002/1

- 7 -

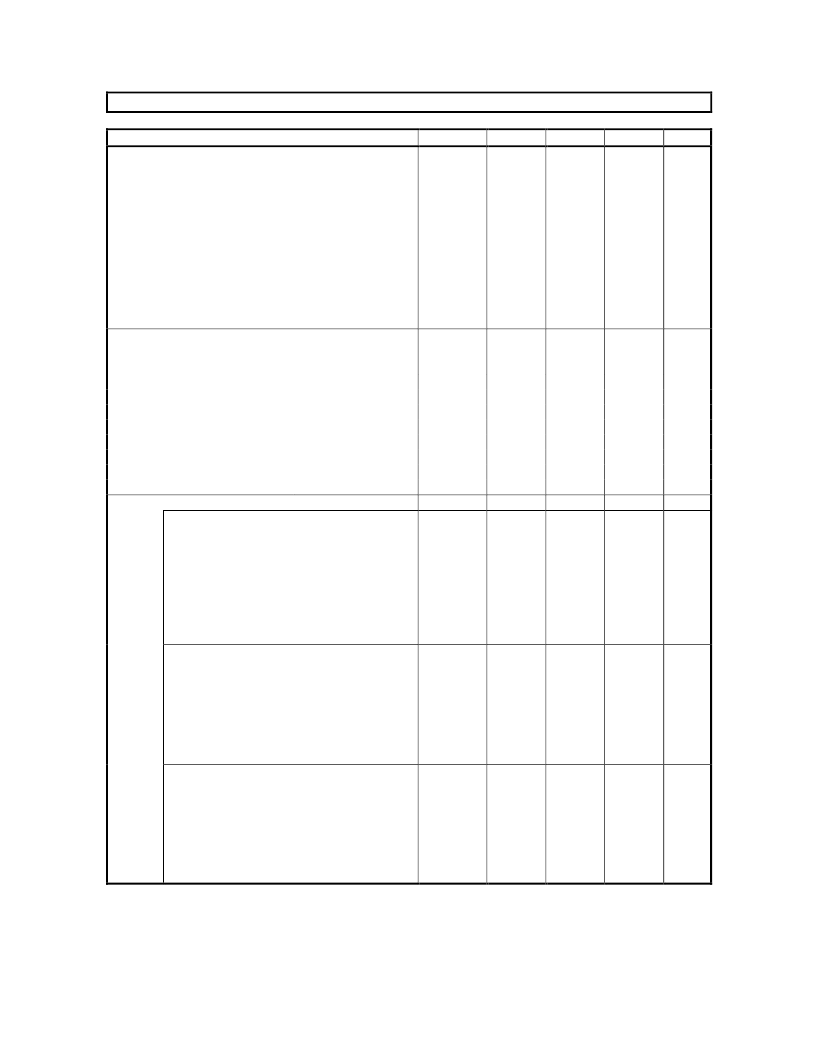

SWITCHING CHARACTERISTICS

(Ta=-40

~

85

°

C; VDD=2.7~3.6V; C

L

=20pF)

Parameter

Symbol

fCLK

dCLK

dCLK

fCLK

dCLK

dCLK

fCLK

dCLK

dCLK

fs

Duty

fs

Duty

Duty

min

2.048

40

28

2.048

40

28

8.192

40

28

8

48

8

48

32

48

325

130

130

45

45

40

25

162

65

65

45

45

40

25

162

65

65

45

45

typ

max

24.576

60

72

24.576

60

72

24.576

60

72

48

52

96

52

96

52

Units

MHz

%

%

MHz

%

%

MHz

%

%

kHz

%

kHz

%

%

kHz

%

%

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Master Clock Input (IMCLK1)

Frequency

Duty Cycle (at FSI > 33kHz)

Duty Cycle (at FSI

≤

33kHz)

Master Clock Input (IMCLK2)

Frequency

Duty Cycle (at FSI > 33kHz)

Duty Cycle (at FSI

≤

33kHz)

Master Clock Input (OMCLK)

Frequency (Note 11)

Duty Cycle (at FSI > 33kHz)

Duty Cycle (at FSI

≤

33kHz)

L/R clock for Input data #1 (ILRCK1)

Frequency

Duty Cycle

L/R clock for Input data #2 (ILRCK2)

Frequency

Duty Cycle

L/R clock for Output data (OLRCK)

Frequency

Duty Cycle

Audio Interface Timing

(Note 14)

Input#1 at Path Mode 0 and 2

Input#2 (Slave Mode) at Path Mode 1

BICK Period

BICK Pulse Width Low

BICK Pulse Width High

LRCK Edge to BICK “

↑

” (Note 15)

BICK “

↑

” to LRCK Edge (Note 15)

SDTI1-2, Hold Time from BICK “

↑

”

SDTI1-2, Setup Time to BICK “

↑

”

Input#2 (Slave Mode) at Path Mode 0 and 3

BICK Period

BICK Pulse Width Low

BICK Pulse Width High

LRCK Edge to BICK “

↑

” (Note 15)

BICK “

↑

” to LRCK Edge (Note 15)

SDTI2, Hold Time from BICK “

↑

”

SDTI2, Setup Time to BICK “

↑

”

Output (Slave Mode)

OBICK Period

OBICK Pulse Width Low

OBICK Pulse Width High

OLRCK Edge to OBICK “

↑

” (Note 15)

OBICK “

↑

” to OLRCK Edge (Note 15)

OLRCK to SDTO (MSB)

OBICK “

↓

” to SDTO

50

50

50

50

50

(Note 12)

Slave Mode

Master Mode

(Note 13)

Slave Mode

Master Mode

fs

Duty

Duty

tBCK

tBCKL

tBCKH

tBLR

tLRB

tSDH

tSDS

tBCK

tBCKL

tBCKH

tBLR

tLRB

tSDH

tSDS

tBCK

tBCKL

tBCKH

tBLR

tLRB

tLRS

tBSD

40

40

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AK42A-024L-033D025SM | Analog IC |

| AK42A-024L-050D033SM | Analog IC |

| AK42A-048L-033D025SM | Analog IC |

| AK42A-048L-050D033SM | Analog IC |

| AK4310VF | Converter IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AK4120VFP-E2 | 制造商:Asahi Kasei Microsystems Co Ltd 功能描述: |

| AK4121 | 制造商:AKM 制造商全稱(chēng):AKM 功能描述:ASYNCHRONOUS SAMPLE RATE CONVERTER |

| AK4121A | 制造商:AKM 制造商全稱(chēng):AKM 功能描述:Asynchronous Sample Rate Converter |

| AK4121A_10 | 制造商:AKM 制造商全稱(chēng):AKM 功能描述:Asynchronous Sample Rate Converter |

| AK4121AVF | 制造商:AKM 制造商全稱(chēng):AKM 功能描述:Asynchronous Sample Rate Converter |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。