- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄166131 > AK4589 (Asahi Kasei Microsystems Co.,Ltd) 2/8 CHANNEL AUDIO CODEC WITH DIR PDF資料下載

參數(shù)資料

| 型號: | AK4589 |

| 廠商: | Asahi Kasei Microsystems Co.,Ltd |

| 元件分類: | Codec |

| 英文描述: | 2/8 CHANNEL AUDIO CODEC WITH DIR |

| 中文描述: | 2 / 8聲道音頻編解碼器迪爾 |

| 文件頁數(shù): | 75/76頁 |

| 文件大小: | 797K |

| 代理商: | AK4589 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁當前第75頁第76頁

ASAHI KASEI

[AK4589]

MS0339-J-00

2004/09

- 8 -

No.

Pin Name

I/O

Function

55

AVDD

-

Analog Power Supply Pin, 4.75V

5.25V

56

AVSS

-

Analog Ground Pin, 0V

57

RX0

I

Receiver Channel 0 Pin (Internal biased pin. Internally biased at PVDD/2)

58

NC

-

No Connect pin

No internal bonding. This pin should be connected to PVSS.

59

RX1

I

Receiver Channel 1 Pin (Internal biased pin. Internally biased at PVDD/2)

60

TEST1

I

Test 1 Pin

This pin should be connected to PVSS.

61

RX2

I

Receiver Channel 2 Pin (Internal biased pin. Internally biased at PVDD/2)

62

NC

-

No Connect pin

No internal bonding. This pin should be connected to PVSS.

63

RX3

I

Receiver Channel 3 Pin (Internal biased pin. Internally biased at PVDD/2)

64

PVSS

-

PLL Ground pin

65

R

-

External Resistor Pin

12k

+/-1% resistor should be connected to PVSS externally.

66

PVDD

-

PLL Power supply Pin, 4.75V

5.25V

67

RX4

I

Receiver Channel 4 Pin (Internal biased pin. Internally biased at PVDD/2)

68

TEST2

I

Test 2 Pin

This pin should be connected to PVSS.

69

RX5

I

Receiver Channel 5 Pin (Internal biased pin. Internally biased at PVDD/2)

70

CAD0

I

Chip Address 0 Pin (ADC/DAC part)

71

RX6

I

Receiver Channel 6 Pin (Internal biased pin. Internally biased at PVDD/2)

72

CAD1

I

Chip Address 1 Pin (ADC/DAC part)

73

RX7

I

Receiver Channel 7 Pin (Internal biased pin. Internally biased at PVDD/2)

74

I2C

I

Control Mode Select Pin.

“L”: 4-wire Serial, “H”: I

2C Bus

75

DAUX2

I

Auxiliary Audio Data Input Pin (DIR/DIT part)

76

VIN

I

V-bit Input Pin for Transmitter Output

77

MCLK

I

Master Clock Input Pin

78

TX0

O

Transmit Channel (Through Data) Output 0 Pin

79

TX1

O

Transmit Channel Output1 pin

When DIT bit = “0”, Through Data.

When DIT bit = “1”, DAUX2 Data.

80

INT0

O

Interrupt 0 Pin

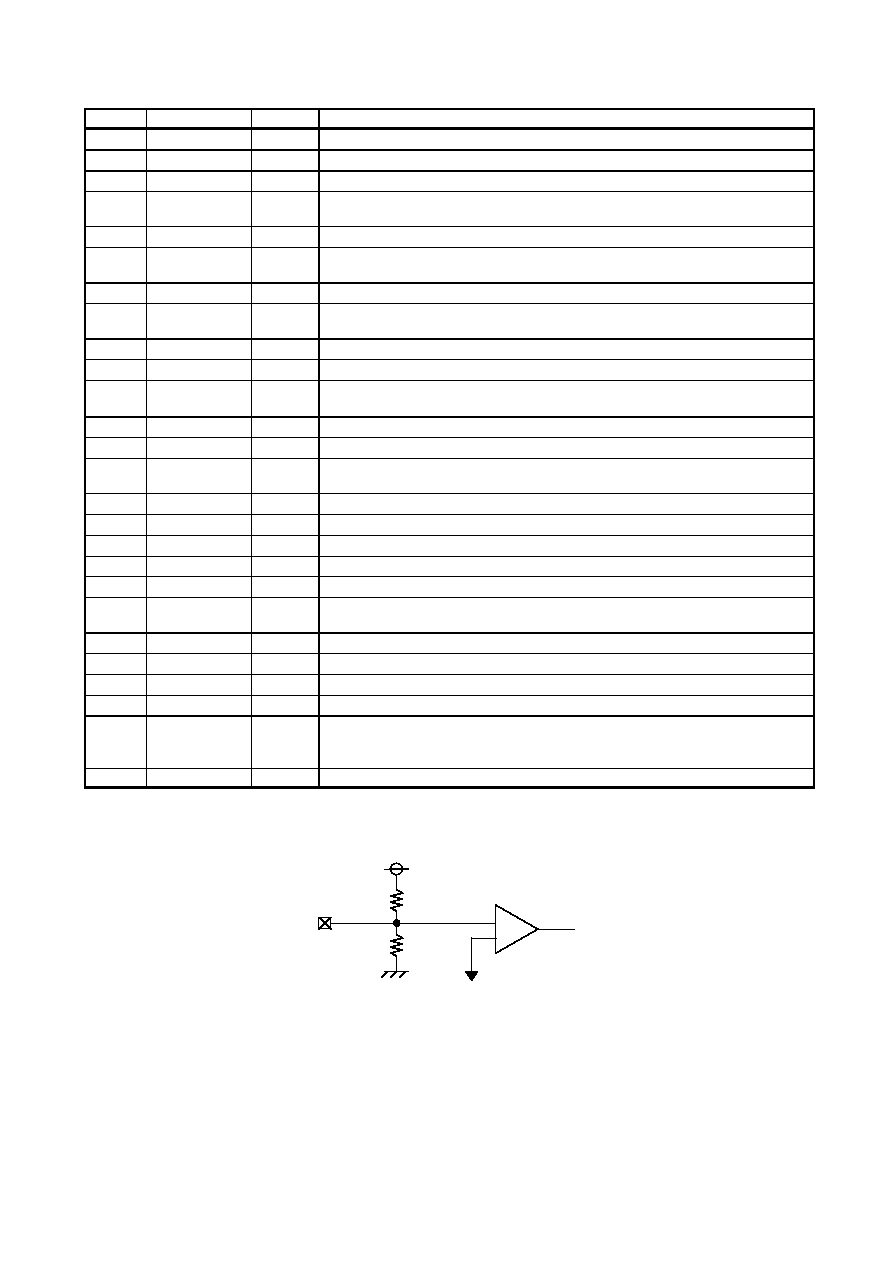

Notes:

(RX0-7, LIN, RIN)

VCOM

PVDD

PVSS

RX pin

20k(typ)

Internal biased pin Circuit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AK4626 | HIGH PERFORMANCE MULTI-CHANNEL AUDIO CODEC |

| AK4641 | 16 BIT CODEC WITH BLUETOOTH INTERFACE |

| AK4641VN | 16 BIT CODEC WITH BLUETOOTH INTERFACE |

| AK4665AEN | SPECIALTY CONSUMER CIRCUIT, QCC32 |

| AK5368192WP-80 | 8M X 36 FAST PAGE DRAM MODULE, 80 ns, SMA72 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AK4589_1 | 制造商:AKM 制造商全稱:AKM 功能描述:2/8-Channel Audio CODEC with DIR |

| AK4589VQ | 制造商:AKM 制造商全稱:AKM 功能描述:2/8-Channel Audio CODEC with DIR |

| AK4591 | 制造商:AKM 制造商全稱:AKM 功能描述:24bit 4ch ADC + 24bit 6ch DAC |

| AK4591VQ | 制造商:AKM 制造商全稱:AKM 功能描述:??¥???????????ˉ??????24bit 4ch ADC 24bit 6ch DAC |

| AK45C | 制造商:ASTEC 制造商全稱:Astec America, Inc 功能描述:36 Vdc to 75 Vdc Inputs, 100 W |

發(fā)布緊急采購,3分鐘左右您將得到回復。