- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295041 > AM24LC08V 2-Wire Serial 8K-Bit (1024 x 8) CMOS Electrically Erasable PROM PDF資料下載

參數(shù)資料

| 型號: | AM24LC08V |

| 英文描述: | 2-Wire Serial 8K-Bit (1024 x 8) CMOS Electrically Erasable PROM |

| 中文描述: | 2線串行8K的位(1024 × 8)的CMOS電可擦除可編程ROM |

| 文件頁數(shù): | 5/10頁 |

| 文件大小: | 202K |

| 代理商: | AM24LC08V |

2-Wire Serial 8K-Bit (1024 x 8) CMOS Electrically Erasable PROM

AM24LC08

Anachip Corp.

www.anachip.com.tw

Rev. A1 Oct 20, 2003

4/10

ATC

Pin Descriptions

Serial Clock (SCL)

The SCL input is used to clock all data into and out

of the device.

Serial Data (SDA)

SDA is a bidirection pin used to transfer data into

and out of the device.

It is an open drain output and may be wire-ORed

with any number of open drain or open collector

outputs. Thus, the SDA bus requires a pull-up

resistor to Vcc (typical 4.7KΩ for 100KHz)

Device Address Inputs (A0, A1, A2)

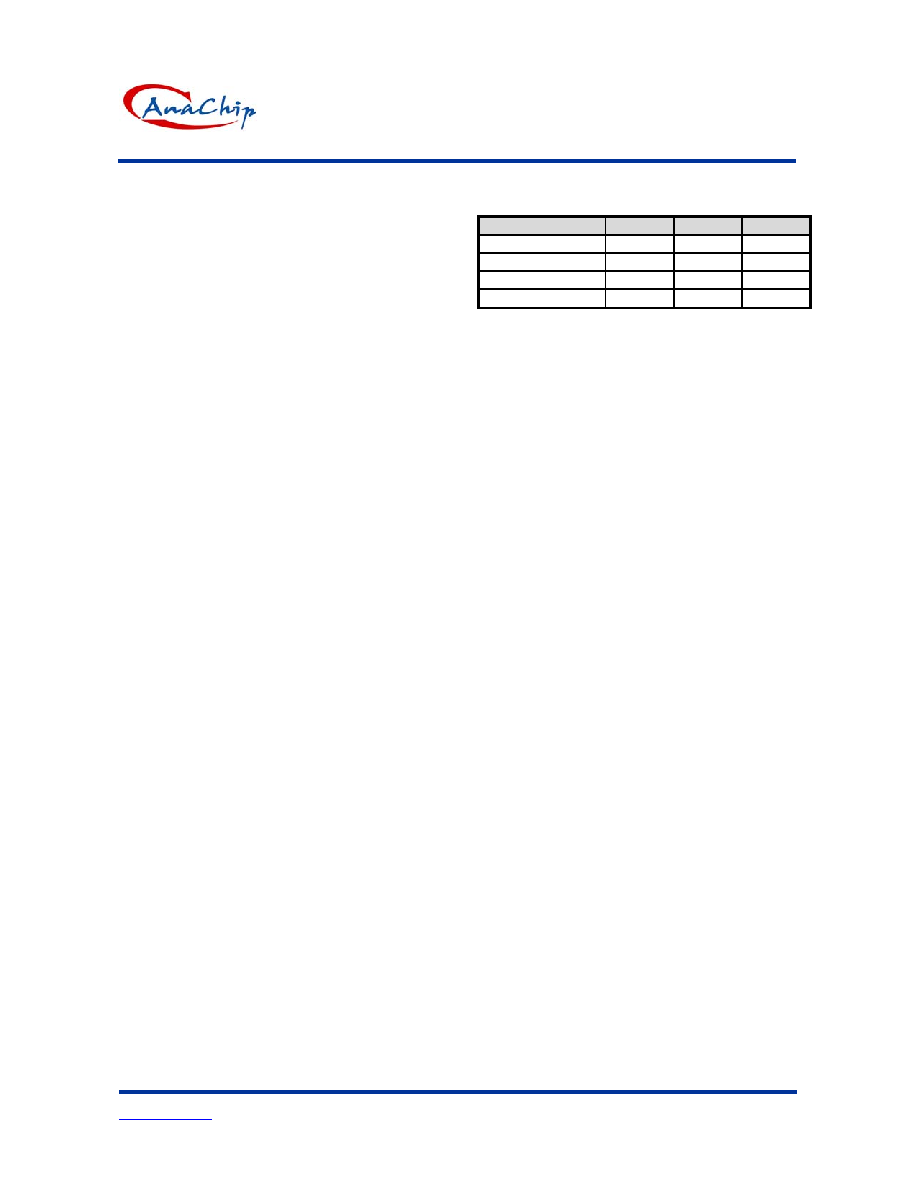

The following table (Table A) shows the active pins

across the AM24LCXX device family.

Table A

Device

A0

A1

A2

AM24LC02

ADR

AM24LC04

XP

ADR

AM24LC08

XP

ADR

AM24LC16

XP

ADR indicates the device address pin.

XP indicates that device address pin don’t care but

refers to an internal PAGE BLOCK memory

segment.

Write Protection (WP)

If WP is connected to Vcc, PROGRAM operation

onto the whole memory will not be executed. READ

operations are possible. If WP is connected to Vss,

normal memory operation is enabled, READ/WRITE

over the entire memory is possible.

Functional Description

Applications

ATC’s electrically erasable programmable read only

memories (EEPROMs) write protect function, two

write modes, three read modes, and a wide variety

of memory size. Typical applications for the I

2C bus

and

AM24LCXX

memories

are

included

in

SANs(small-area-networks),

stereos,

televisions,

automobiles and other scaled-down systems that

don't require tremendous speeds but instead cost

efficiency and design simplicity.

Endurance and Data Retention

The AM24LC08 is designed for applications requiring

up to 1M programming cycles (BYTE WRITE and

PAGE WRITE). It provides 40 years of secure data

retention without power.

Device Operation

The AM24LC08 support a bi-directional bus oriented

protocol. The protocol defines any device that sends

data onto the bus as a transmitter and the receiving

device as the receiver. The device controlling the

transfer is the master and the device that is

controlled is the slave. The master will always

initiate data transfers and provide the clock for both

transmit and receive operations. Therefore, the

AM24LC08 is considered a slave in all applications.

Clock and Data Conventions

Data states on the SDA line can change only during

SCL LOW. SDA state changes during SCL HIGH

are reserved for indicating start and stop conditions.

(Shown in Figures 1 and 2)

Start Condition

A HIGH to LOW transition of the SDA line while the

clock (SCL) is HIGH determines a START condition.

All commands must be preceded by a START

condition. (Shown in Figure 2)

Stop Condition

A LOW to HIGH transition of the SDA line while the

clock (SCL) is HIGH determines a STOP condition.

All operations must be ended with a STOP condition.

(Shown in Figure 2)

Acknowledge

Each receiving device, when addressed, is obliged

to generate an acknowledge after the reception of

each byte. The master device must generate an

extra clock pulse which is associated with this

acknowledge bit. The device that acknowledges,

has to pull down the SDA line during the

acknowledge clock pulse in such a way that the

SDA line is stable LOW during the HIGH period of

the acknowledge related clock pulse. Of course,

setup and hold times must be taken into account. A

master must signal an end of data to the slave by

not generating an acknowledge bit on the last byte

that has been clocked out of the slave. In this case,

the slave must leave the data line HIGH to enable

the master to generate the STOP condition. (Shown

in Figure 3)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM24LC08VN | 2-Wire Serial 8K-Bit (1024 x 8) CMOS Electrically Erasable PROM |

| AM24LC08VS | 2-Wire Serial 8K-Bit (1024 x 8) CMOS Electrically Erasable PROM |

| AM24LC16 | 2-Wire Serial 16K-bits (2048 x 8) CMOS Electrically Erasable PROM |

| AM24LC16I | 2-Wire Serial 16K-bits (2048 x 8) CMOS Electrically Erasable PROM |

| AM24LC16N | 2-Wire Serial 16K-bits (2048 x 8) CMOS Electrically Erasable PROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM24LC08VN | 制造商:ANACHIP 制造商全稱:Anachip Corp 功能描述:2-Wire Serial 8K-Bit (1024 x 8) CMOS Electrically Erasable PROM |

| AM24LC08VNA | 制造商:ANACHIP 制造商全稱:Anachip Corp 功能描述:2-Wire Serial 8K-Bit (1024 x 8) CMOS Electrically Erasable PROM |

| AM24LC08VS | 制造商:ANACHIP 制造商全稱:Anachip Corp 功能描述:2-Wire Serial 8K-Bit (1024 x 8) CMOS Electrically Erasable PROM |

| AM24LC08VSA | 制造商:ANACHIP 制造商全稱:Anachip Corp 功能描述:2-Wire Serial 8K-Bit (1024 x 8) CMOS Electrically Erasable PROM |

| AM24LC16 | 制造商:ANACHIP 制造商全稱:Anachip Corp 功能描述:2-Wire Serial 4K-Bit (512 x 8) CMOS Electrically Erasable PROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。