- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366528 > AM29SL160CB-100EEN (Advanced Micro Devices, Inc.) 16 Megabit CMOS 1.8 Volt-only Super Low Voltage Flash Memory PDF資料下載

參數(shù)資料

| 型號(hào): | AM29SL160CB-100EEN |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | 16 Megabit CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| 中文描述: | 16兆位的CMOS 1.8伏只超低電壓快閃記憶體 |

| 文件頁數(shù): | 20/52頁 |

| 文件大小: | 1232K |

| 代理商: | AM29SL160CB-100EEN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

20

Am29SL160C

November 1, 2004

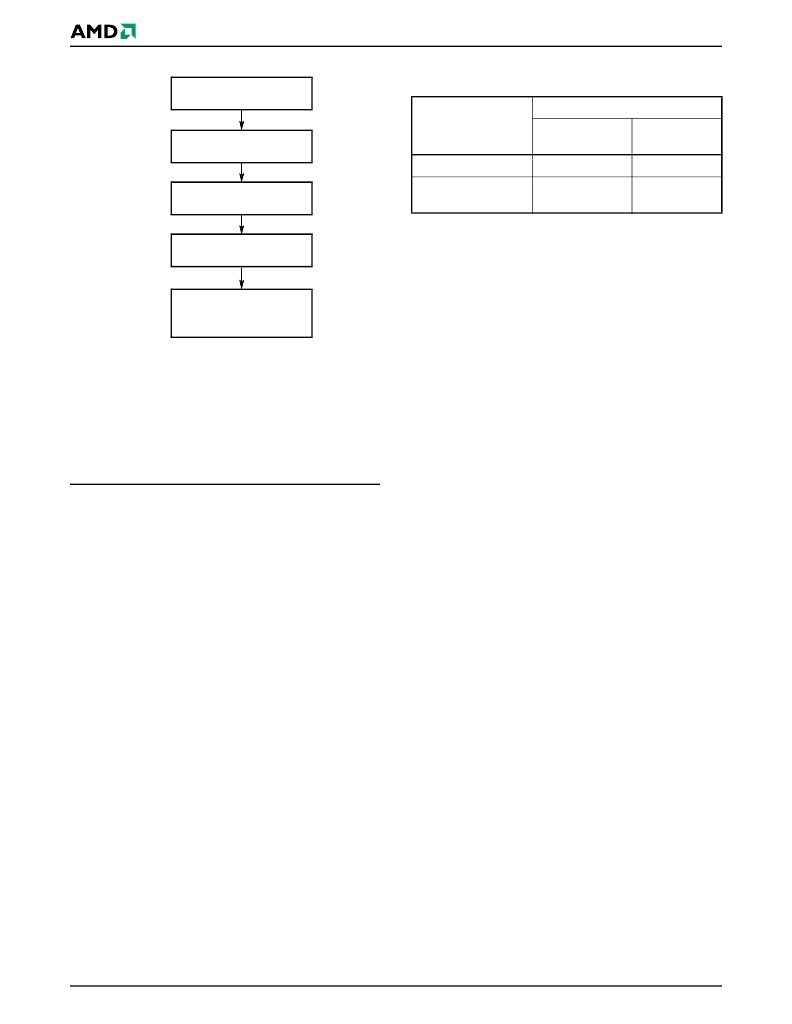

Figure 2.

Temporary Sector Unprotect Operation

Secured Silicon (SecSi) Sector Flash

Memory Region

The Secured Silicon (SecSi) Sector is a flash memory

region that enables permanent part identification

through an Electronic Serial Number (ESN). The SecSi

Sector in this device is 256 bytes in length. The device

contains a SecSi Sector indicator bit that allows the

system to determine whether or not the SecSi Sector

was factory locked. This indicator bit is permanently set

at the factory and cannot be changed, which prevents

a factory-locked part from being cloned.

AMD offers this device only with the SecSi Sector

factory serialized and locked. The first sixteen bytes of

the SecSi Sector contain a random ESN. To utilize the

remainder SecSi Sector space, customers must

provide their code to AMD through AMD’s Express

Flash service. The factory will program and perma-

nently protect the SecSi Sector (in addition to

programming and protecting the remainder of the

device as required).

The system can read the SecSi Sector by writing the

Enter SecSi Sector command sequence (see

“Enter

SecSi Sector/Exit SecSi Sector Command Sequence”

on page 24

).

Table 7, on page 20

shows the layout for

the SecSi Sector.

Table 7.

SecSi Sector Addresses

The device continues to read from the SecSi Sector

until the system issues the Exit SecSi Sector command

sequence, or until power is removed from the device.

On power-up, or following a hardware reset, the device

reverts to sending commands to the boot sectors.

Hardware Data Protection

The command sequence requirement of unlock cycles

for programming or erasing provides data protection

against inadvertent writes (refer to

Table 12, on

page 28

for command definitions). In addition, the fol-

lowing hardware data protection measures prevent

accidental erasure or programming, which might other-

wise be caused by spurious system level signals during

V

CC

power-up and power-down transitions, or from

system noise.

Low V

CC

Write Inhibit

When V

CC

is less than V

LKO

, the device does not accept

any write cycles. This protects data during V

CC

power-up and power-down. The command register and

all internal program/erase circuits are disabled, and the

device resets. Subsequent writes are ignored until V

CC

is greater than V

LKO

. The system must provide the

proper signals to the control pins to prevent uninten-

tional writes when V

CC

is greater than V

LKO

.

Write Pulse “Glitch” Protection

Noise pulses of less than 5 ns (typical) on OE#, CE# or

WE# do not initiate a write cycle.

Logical Inhibit

Write cycles are inhibited by holding any one of OE# =

V

IL

, CE# = V

IH

or WE# = V

IH

. To initiate a write cycle,

CE# and WE# must be a logical zero while OE# is a

logical one.

Power-Up Write Inhibit

If WE# = CE# = V

IL

and OE# = V

IH

during power up, the

device does not accept commands on the rising edge

of WE#. The internal state machine is automatically

reset to reading array data on power-up.

START

Perform Erase or

Program Operations

RESET# = V

IH

Temporary Sector

Unprotect Completed

(Note 2)

RESET# = V

ID

(Note 1)

Notes:

1. All protected sectors unprotected. (If WP#/ACC = V

IL

,

the outermost sectors remain protected)

2. All previously protected sectors are protected once

again.

Description

Address Range

Word Mode

(x16)

Byte Mode (x8)

16-byte random ESN

00–07h

000–00Fh

User-defined code or

factory erased (all 1s)

08–7Fh

010–0FFh

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM29SL160CB-100EFN | 16 Megabit CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| AM29SL160CB-100EIN | 16 Megabit CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| AM29SL160CB-100WCCN | 16 Megabit CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| AM29SL160CB-100WCDN | 16 Megabit CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| AM29SL160CB-100WCEN | 16 Megabit CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM29SL160CT-100EIN | 制造商:Advanced Micro Devices 功能描述: |

| AM29SL800DB120WCI | 制造商:Spansion 功能描述:FLASH PARALLEL 1.8V 8MBIT 1MX8/512KX16 120NS 48FBGA - Trays |

| AM29SL800DB90WAD | 制造商:Spansion 功能描述: |

| AM29X305ADC | 制造商:Advanced Micro Devices 功能描述:Microprocessor, 8 Bit, 50 Pin, Ceramic, DIP |

| AM2A016 | 制造商:MAG-LITE 功能描述:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。