- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366531 > AM29SL800CT120EI (ADVANCED MICRO DEVICES INC) 8 Megabit (1 M x 8-Bit/512 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory PDF資料下載

參數(shù)資料

| 型號: | AM29SL800CT120EI |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | PROM |

| 英文描述: | 8 Megabit (1 M x 8-Bit/512 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| 中文描述: | 1M X 8 FLASH 1.8V PROM, 120 ns, PDSO48 |

| 封裝: | TSOP-48 |

| 文件頁數(shù): | 14/41頁 |

| 文件大小: | 549K |

| 代理商: | AM29SL800CT120EI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

14

Am29SL800C

P R E L I M I N A R Y

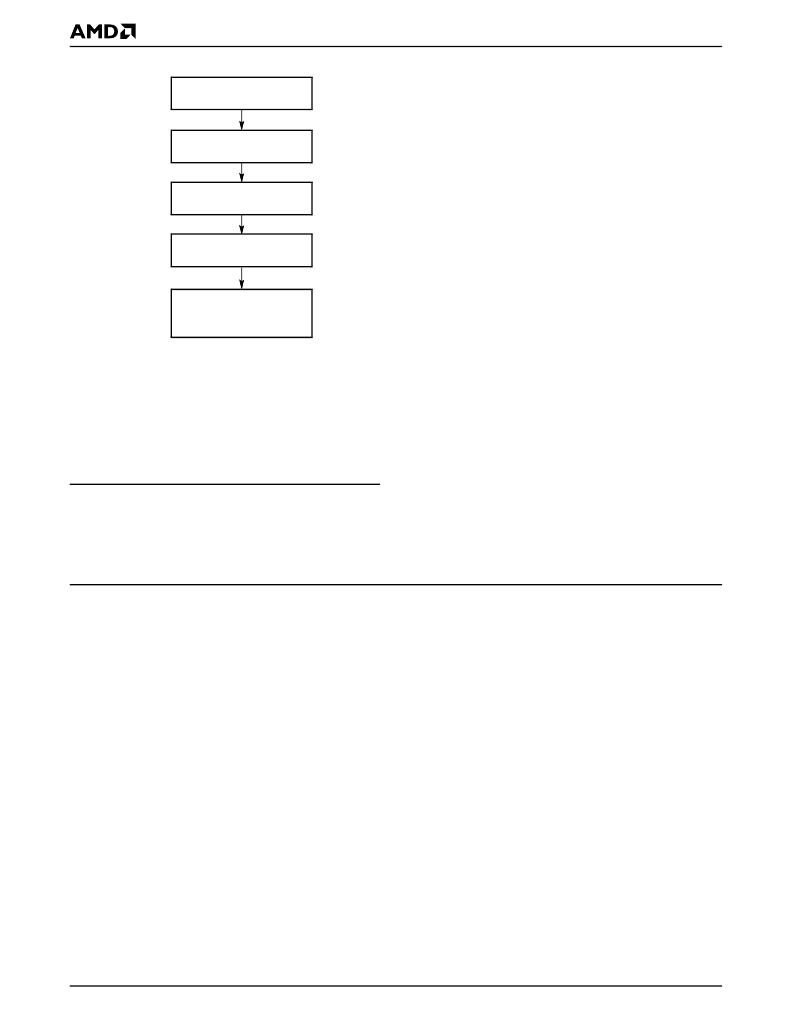

Figure 2.

Temporary Sector Unprotect Operation

Hardware Data Protection

The command sequence requirement of unlock cycles

for programming or erasing provides data protection

against inadvertent writes (refer to Table 5 for com-

mand definitions). In addition, the following hardware

data protection measures prevent accidental erasure

or programming, which might otherwise be caused by

spurious system level signals during V

CC

power-up and

power-down transitions, or from system noise.

Low V

CC

Write Inhibit

When V

CC

is less than V

LKO

, the device does not ac-

cept any write cycles. This protects data during V

CC

power-up and power-down. The command register and

all internal program/erase circuits are disabled, and the

device resets. Subsequent writes are ignored until V

CC

is greater than V

LKO

. The system must provide the

proper signals to the control pins to prevent uninten-

tional writes when V

CC

is greater than V

LKO

.

Write Pulse “Glitch” Protection

Noise pulses of less than 5 ns (typical) on OE#, CE# or

WE# do not initiate a write cycle.

Logical Inhibit

Write cycles are inhibited by holding any one of OE#

= V

IL

, CE# = V

IH

or WE# = V

IH

. To initiate a write cy-

cle, CE# and WE# must be a logical zero while OE#

is a logical one.

Power-Up Write Inhibit

If WE# = CE# = V

IL

and OE# = V

IH

during power

up, the device does not accept commands on the

rising edge of WE#. The internal state machine is

automatically reset to reading array data on

power-up.

COMMAND DEFINITIONS

Writing specific address and data commands or se-

quences into the command register initiates device op-

erations. Table 5 defines the valid register command

sequences. Writing

incorrect

address and data val-

ues

or writing them in the

improper sequence

resets

the device to reading array data.

All addresses are latched on the falling edge of WE# or

CE#, whichever happens later. All data is latched on

the rising edge of WE# or CE#, whichever happens

first. Refer to the appropriate timing diagrams in the

“AC Characteristics” section.

Reading Array Data

The device is automatically set to reading array data

after device power-up. No commands are required to

retrieve data. The device is also ready to read array

data after completing an Embedded Program or Em-

bedded Erase algorithm.

After the device accepts an Erase Suspend com-

mand, the device enters the Erase Suspend mode.

The system can read array data using the standard

read timings, except that if it reads at an address

within erase-suspended sectors, the device outputs

status data. After completing a programming opera-

tion in the Erase Suspend mode, the system may

once again read array data with the same exception.

See “Erase Suspend/Erase Resume Commands” for

more information on this mode.

The system

must

issue the reset command to re-ena-

ble the device for reading array data if DQ5 goes high,

or while in the autoselect mode. See the “Reset Com-

mand” section, next.

See also “Requirements for Reading Array Data” in the

“Device Bus Operations” section for more information.

The Read Operations table provides the read parame-

ters, and Figure 13 shows the timing diagram.

Reset Command

Writing the reset command to the device resets the de-

vice to reading array data. Address bits are don’t care

for this command.

START

Perform Erase or

Program Operations

RESET# = V

IH

Temporary Sector

Unprotect Completed

(Note 2)

RESET# = V

ID

(Note 1)

Notes:

1. All protected sectors unprotected.

2. All previously protected sectors are protected once

again.

22230A-6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Am29SL800CT120EIB | 8 Megabit (1 M x 8-Bit/512 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| AM29SL800CT120FC | Quad 2-Input AND Gates 14-PDIP -55 to 125 |

| Am29SL800CT120FCB | 8 Megabit (1 M x 8-Bit/512 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

| AM29SL800CT120FI | Quad 2-Input AND Gates 14-SOIC -55 to 125 |

| Am29SL800CT120FIB | 8 Megabit (1 M x 8-Bit/512 K x 16-Bit) CMOS 1.8 Volt-only Super Low Voltage Flash Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM29SL800DB120WCI | 制造商:Spansion 功能描述:FLASH PARALLEL 1.8V 8MBIT 1MX8/512KX16 120NS 48FBGA - Trays |

| AM29SL800DB90WAD | 制造商:Spansion 功能描述: |

| AM29X305ADC | 制造商:Advanced Micro Devices 功能描述:Microprocessor, 8 Bit, 50 Pin, Ceramic, DIP |

| AM2A016 | 制造商:MAG-LITE 功能描述:Bulk |

| AM2A026 | 制造商:MAG-LITE 功能描述:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。