- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄253907 > AM41PDS3224DB11FS (SPANSION LLC) SPECIALTY MEMORY CIRCUIT, PBGA73 PDF資料下載

參數(shù)資料

| 型號(hào): | AM41PDS3224DB11FS |

| 廠商: | SPANSION LLC |

| 元件分類: | 存儲(chǔ)器 |

| 英文描述: | SPECIALTY MEMORY CIRCUIT, PBGA73 |

| 封裝: | 8 X 11.60 MM, FBGA-73 |

| 文件頁數(shù): | 5/59頁 |

| 文件大小: | 1072K |

| 代理商: | AM41PDS3224DB11FS |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

12

Am41PDS3224D

May 13, 2002

P R E L IMINARY

FLASH DEVICE BUS OPERATIONS

Requirements for Reading Array Data

To read array data from the outputs, the system must

drive the CE#f and OE# pins to V

IL. CE#f is the power

control and selects the device. OE# is the output con-

trol and gates array data to the output pins. WE#

should remain at V

IH.

The internal state machine is set for reading array data

upon device power-up, or after a hardware reset. This

ensures that no spurious alteration of the memory

content occurs during the power transition. No com-

mand is necessary in this mode to obtain array data.

Standard microprocessor read cycles that assert valid

addresses on the device address inputs produce valid

data on the device data outputs. Each bank remains

enabled for read access until the command register

contents are altered.

See “Requirements for Reading Array Data” for more

information. Refer to the AC Read-Only Operations

table for timing specifications and to Figure 15 for the

timing diagram. I

CC1 in the DC Characteristics table

represents the active current specification for reading

array data.

Read Mode

Random Read (Non-Page Mode Read)

The device has two control functions which must be

satisfied in order to obtain data at the outputs. CE# is

the power control and should be used for device selec-

tion. OE# is the output control and should be used to

gate data to the output pins if the device is selected.

Address access time (t

ACC) is equal to the delay from

stable addresses to valid output data. The chip enable

access time (t

CE) is the delay from the stable ad-

dresses and stable CE# to valid data at the output

pins. The output enable access time is the delay from

the falling edge of OE# to valid data at the output pins

(assuming the addresses have been stable for at least

t

ACC–tOE time).

Page Mode Read

The device is capable of fast Page mode read and is

compatible with the Page mode Mask ROM read oper-

ation. This mode provides faster read access speed

for random locations within a page. The Page size of

the device is 4 words. The appropriate Page is se-

lected by the higher address bits A20–A0 and the LSB

bits A1–A0 determine the specific word within that

page. This is an asynchronous operation with the mi-

croprocessor supplying the specific word location.

The random or initial page access is equal to t

ACC or

t

CE and subsequent Page read accesses (as long as

the locations specified by the microprocessor fall

within that Page) are equivalent to t

PACC. When CE# is

deasserted and reasserted for a subsequent access,

the access time is t

ACC or tCE. Here again, CE# selects

the device and OE# is the output control and should be

used to gate data to the output pins if the device is se-

lected. Fast Page mode accesses are obtained by

keeping A20–A2 constant and changing A1–A0 to se-

lect the specific word within that page. See Figure 16

for timing specifications.

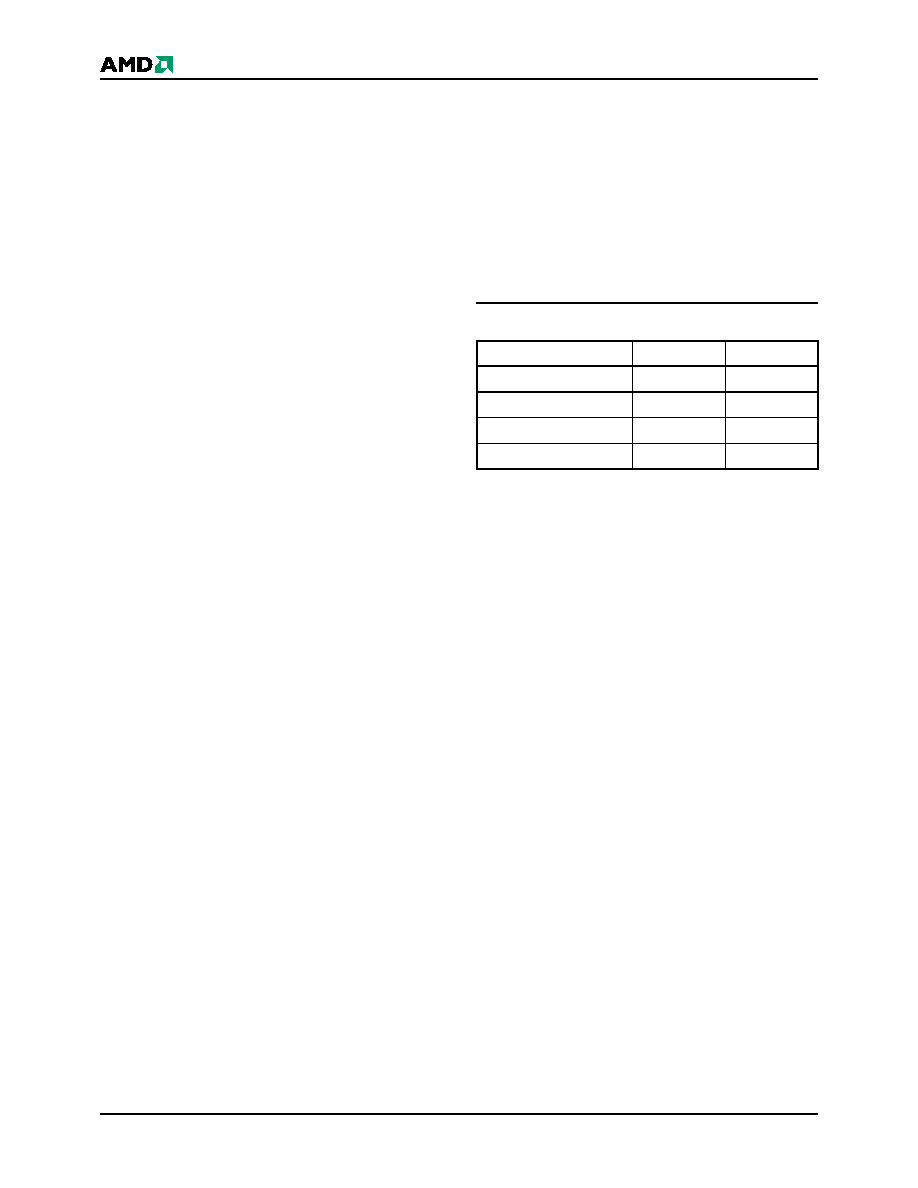

The following table determines the specific word within

the selected page:

Table 3.

Page Word Mode

Writing Commands/Command Sequences

To write a command or command sequence (which in-

cludes programming data to the device and erasing

sectors of memory), the system must drive WE# and

CE# to V

IL, and OE# to VIH.

The device features an Unlock Bypass mode to facil-

itate faster programming. Once the device enters the

Unlock Bypass mode, only two write cycles are re-

quired to program a word, instead of four. The “Word

Program Command Sequence” section has details on

programming data to the device using both standard

and Unlock Bypass command sequences.

An erase operation can erase one sector, multiple sec-

tors, or the entire device. Table 3 indicates the address

space that each sector occupies.

CC2f in the DC Characteristics table represents the ac-

tive current specification for the write mode. The Mea-

Characteristics. section contains timing specification

tables and timing diagrams for write operations.

Accelerated Program Operation

The device offers accelerated program operations

through the ACC function. This is one of two functions

provided by the WP#/ACC pin. This function is prima-

rily intended to allow faster manufacturing throughput

at the factory.

If the system asserts V

HH on this pin, the device auto-

matically enters the aforementioned Unlock Bypass

mode, temporarily unprotects any protected sectors,

Word

A1

A0

Word 0

0

Word 1

0

1

Word 2

1

0

Word 3

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM29F017D-120FD | 2M X 8 FLASH 5V PROM, 120 ns, PDSO48 |

| AM29LV004T-70RFF | 512K X 8 FLASH 3V PROM, 70 ns, PDSO40 |

| AM29LV004T-80EF | 512K X 8 FLASH 3V PROM, 80 ns, PDSO40 |

| AT28C1024-20BM/883 | 64K X 16 EEPROM 5V, 200 ns, CDIP40 |

| AM99C641-45/LMC | 64K X 1 STANDARD SRAM, 45 ns, CQCC22 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM41PDS3224DB11IS | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:32 Megabit (2 M x 16-Bit) CMOS 1.8 Volt-only, Simultaneous Operation, Page Mode Flash Memory and 4 Mbit (512 K x 8-Bit/256 K x 16-Bit) Static RAM |

| AM41PDS3224DB11IT | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:32 Megabit (2 M x 16-Bit) CMOS 1.8 Volt-only, Simultaneous Operation, Page Mode Flash Memory and 4 Mbit (512 K x 8-Bit/256 K x 16-Bit) Static RAM |

| AM41PDS3224DB35IS | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:32 Megabit (2 M x 16-Bit) CMOS 1.8 Volt-only, Simultaneous Operation, Page Mode Flash Memory and 4 Mbit (512 K x 8-Bit/256 K x 16-Bit) Static RAM |

| AM41PDS3224DB35IT | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:32 Megabit (2 M x 16-Bit) CMOS 1.8 Volt-only, Simultaneous Operation, Page Mode Flash Memory and 4 Mbit (512 K x 8-Bit/256 K x 16-Bit) Static RAM |

| AM41PDS3224DB40IS | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:32 Megabit (2 M x 16-Bit) CMOS 1.8 Volt-only, Simultaneous Operation, Page Mode Flash Memory and 4 Mbit (512 K x 8-Bit/256 K x 16-Bit) Static RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。