- 您現在的位置:買賣IC網 > PDF目錄362307 > AMD29DL161DB120EI EEPROM PDF資料下載

參數資料

| 型號: | AMD29DL161DB120EI |

| 元件分類: | EEPROM |

| 英文描述: | EEPROM |

| 中文描述: | EEPROM的 |

| 文件頁數: | 38/53頁 |

| 文件大小: | 1167K |

| 代理商: | AMD29DL161DB120EI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

38

Am29DL16xD

July 29, 2002

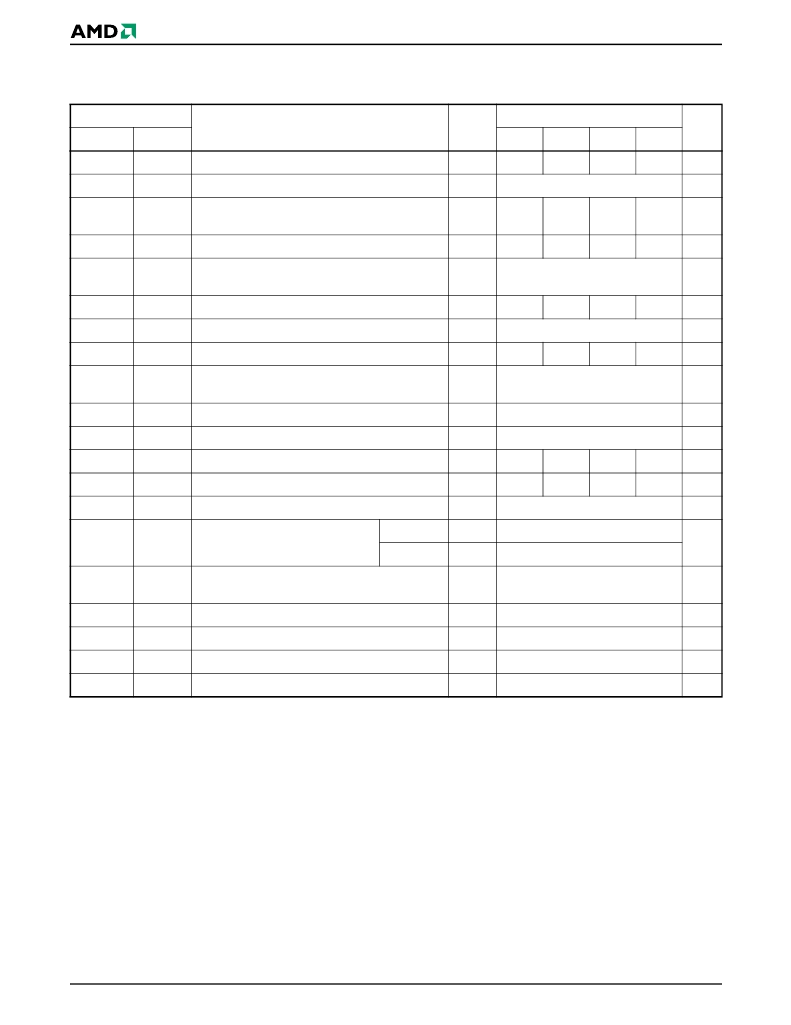

AC CHARACTERISTICS

Erase and Program Operations

Notes:

1. Not 100% tested.

2. See the “Erase And Programming Performance” section for more information.

Parameter

Speed Options

JEDEC

Std

Description

70

80

90

120

Unit

t

AVAV

t

WC

Write Cycle Time (Note 1)

Min

70

80

90

120

ns

t

AVWL

t

AS

Address Setup Time

Min

0

ns

t

ASO

Address Setup Time to OE# low during toggle bit

polling

Min

15

15

15

15

ns

t

WLAX

t

AH

Address Hold Time

Min

45

45

45

50

ns

t

AHT

Address Hold Time From CE# or OE# high

during toggle bit polling

Min

0

ns

t

DVWH

t

DS

Data Setup Time

Min

35

35

45

50

ns

t

WHDX

t

DH

Data Hold Time

Min

0

ns

t

OEPH

Output Enable High during toggle bit polling

Min

20

20

20

20

ns

t

GHWL

t

GHWL

Read Recovery Time Before Write

(OE# High to WE# Low)

Min

0

ns

t

ELWL

t

CS

CE# Setup Time

Min

0

ns

t

WHEH

t

CH

CE# Hold Time

Min

0

ns

t

WLWH

t

WP

Write Pulse Width

Min

30

30

35

50

ns

t

WHDL

t

WPH

Write Pulse Width High

Min

30

30

30

30

ns

t

SR/W

Latency Between Read and Write Operations

Min

0

ns

t

WHWH1

t

WHWH1

Programming Operation (Note 2)

Byte

Typ

5

μs

Word

Typ

7

t

WHWH1

t

WHWH1

Accelerated Programming Operation,

Word or Byte (Note 2)

Typ

4

μs

t

WHWH2

t

WHWH2

Sector Erase Operation (Note 2)

Typ

0.7

sec

t

VCS

V

CC

Setup Time (Note 1)

Min

50

μs

t

RB

Write Recovery Time from RY/BY#

Min

0

ns

t

BUSY

Program/Erase Valid to RY/BY# Delay

Min

90

ns

相關PDF資料 |

PDF描述 |

|---|---|

| AMD29DL161DB120PCI | EEPROM |

| AMD29DL161DB120WCI | EEPROM |

| AMD29DL162DT90WCI | EEPROM |

| AMD29DL163DB120EI | EEPROM |

| AMD29DL163DB120PCI | EEPROM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AMD29DL161DB120PCI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| AMD29DL161DB120WCI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| AMD29DL161DB70EI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| AMD29DL161DB70PCI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| AMD29DL161DB70WCI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復。