- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362444 > AS5SS128K36DQ-10 x36 Fast Synchronous SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | AS5SS128K36DQ-10 |

| 英文描述: | x36 Fast Synchronous SRAM |

| 中文描述: | x36快速同步SRAM |

| 文件頁(yè)數(shù): | 3/16頁(yè) |

| 文件大小: | 224K |

| 代理商: | AS5SS128K36DQ-10 |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

SRAM

AS5SS128K36

Austin Semiconductor, Inc.

AS5SS128K36

Rev. 2.0 12/00

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

3

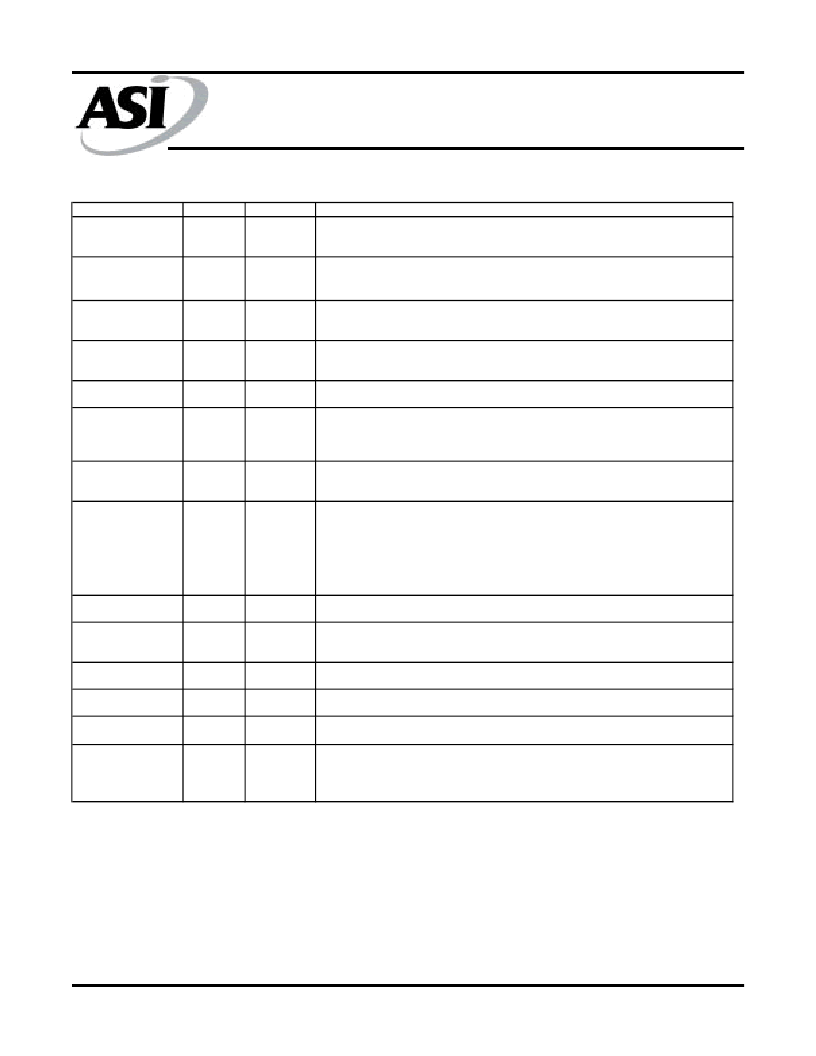

PIN DESCRIPTIONS (continued)

TQFP PINS

SYMBOL

64

TYPE

Input

DESCRIPTION

ZZ

Snooze Enable: This active HIGH, asynchronous input causes the device to enter a

low-power standby mode in which all data in the memory array is retained. When ZZ

is active, all other inputs are ignored.

Clock: This signal registers the address, data, chip enables, byte write enables and

burst control inputs on its rising edge. All synchronous inputs must meet setup and

hold times around the clock's rising edge.

Synchronous Chip Enable: These active LOW inputs are used to enable the device

and are sampled only when a new external address is loaded (ADV/LD\ LOW). CE2\

can be used for memory depth expansion.

Synchronous Enable: This active HIGH input is used to enable the device and is

sampled only when a new external address is loaded (ADV/LD\ LOW). This input can

be used for memory depth expansion.

Output Enable: This active LOW, asynchronous inputs enables the data I/O output

drivers. G\ is the JEDEC-standard term for OE\.

Synchronous Address Advance/Load: When HIGH, this input is used to advance the

internal burst counter, controlling burst access after the external address is loaded.

When ADV/LD\ is HIGH, R/W\ is ignored. A LOW on ADV/LD\ clocks a new address

at the CLK rising edge.

Mode: This inputs selects the burst sequence. A LOW on this pin selects linear burst.

NC or HIGH on this pin selects interleaved burst. Do not alter input state while device

is operating. LBO\ is the JEDEC-standard term for MODE.

Input/Output SRAM Data I/Os: Byte "a" is DQa pins; Byte "b" is DQb pins; Byte "c" is DQc pins;

Byte "d" is DQd pins. Input data must meet setup and hold times around the rising

edge CLK.

89

CLK

Input

98, 92

CE\, CE2\

Input

97

CE2

Input

86

OE\

(G\)

ADV/LD\

Input

85

Input

31

MODE

(LBO\)

Input

(a) 51, 52, 53, 56-59,

62, 63

(b) 68, 69, 72-75, 78,

79, 80

(c)1, 2, 3, 6-9, 12, 13

(d) 18, 19, 22-25, 28,

29, 30

15, 16, 41, 65, 91

DQa

DQb

DQc

DQd

V

DD

Supply

Power Supply: See DC Electrical Characteristics and Operating Conditions for range.

5, 10, 14, 17, 21, 26

40, 55, 60, 66, 67, 71

76, 90

4, 11, 20, 27, 54, 61

70, 77

38, 39, 42, 43, 83, 84

64

38, 39, 42, 43

Vss

Ground

Ground: GND

V

DD

Q

Supply

Isolated Output Buffer Supply:

Conditions for range.

No Connect: These pins can be left floating or connected to GND to minimize thermal

impedance.

Do Not Use: These signals may with be unconnected or wired to GND to

minimize thermal impedance.

No Function: These pins are internally connected to the die and will have the

capacitance of an input pin. It is allowable to leave these pins unconnected or

driven by signals. Pins 83 and 84 are reserved for address expansion.

See DC Electrical Characteristics and Operating

NC

----

DNU

----

83, 84

NF

----

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AS5SS128K36DQ-11 | x36 Fast Synchronous SRAM |

| AS5SS128K36DQ-11IT | x36 Fast Synchronous SRAM |

| AS6UA25617 | 1.65V to 3.6V 256K x 16 Intelliwatt low power CMOS SRAM with two chip enables |

| AS6UA51216 | 1.65V to 3.6V 512K x 16 Intelliwatt low power CMOS SRAM with one chip enable |

| AS6VA2516-TC | x16 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AS5SS128K36DQ-11 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Fast Synchronous SRAM |

| AS5SS128K36DQ-11/IT | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:128K x 36 SSRAM SYNCHRONOUS ZBL SRAM FLOW-THRU OUTPUT |

| AS5SS128K36DQ-11/XT | 制造商:AUSTIN 制造商全稱:Austin Semiconductor 功能描述:128K x 36 SSRAM SYNCHRONOUS ZBL SRAM FLOW-THRU OUTPUT |

| AS5SS128K36DQ-11IT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Fast Synchronous SRAM |

| AS5SS128K36DQ-11XT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Fast Synchronous SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。